edfas.org

edfas.org

21

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 18 NO. 2

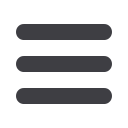

exhibit approximately an order of magnitude decrease

in soft errors compared to planar transistors at the same

technology node. This is consistent with the experimen-

tally observed decrease in soft error in Fig. 3.

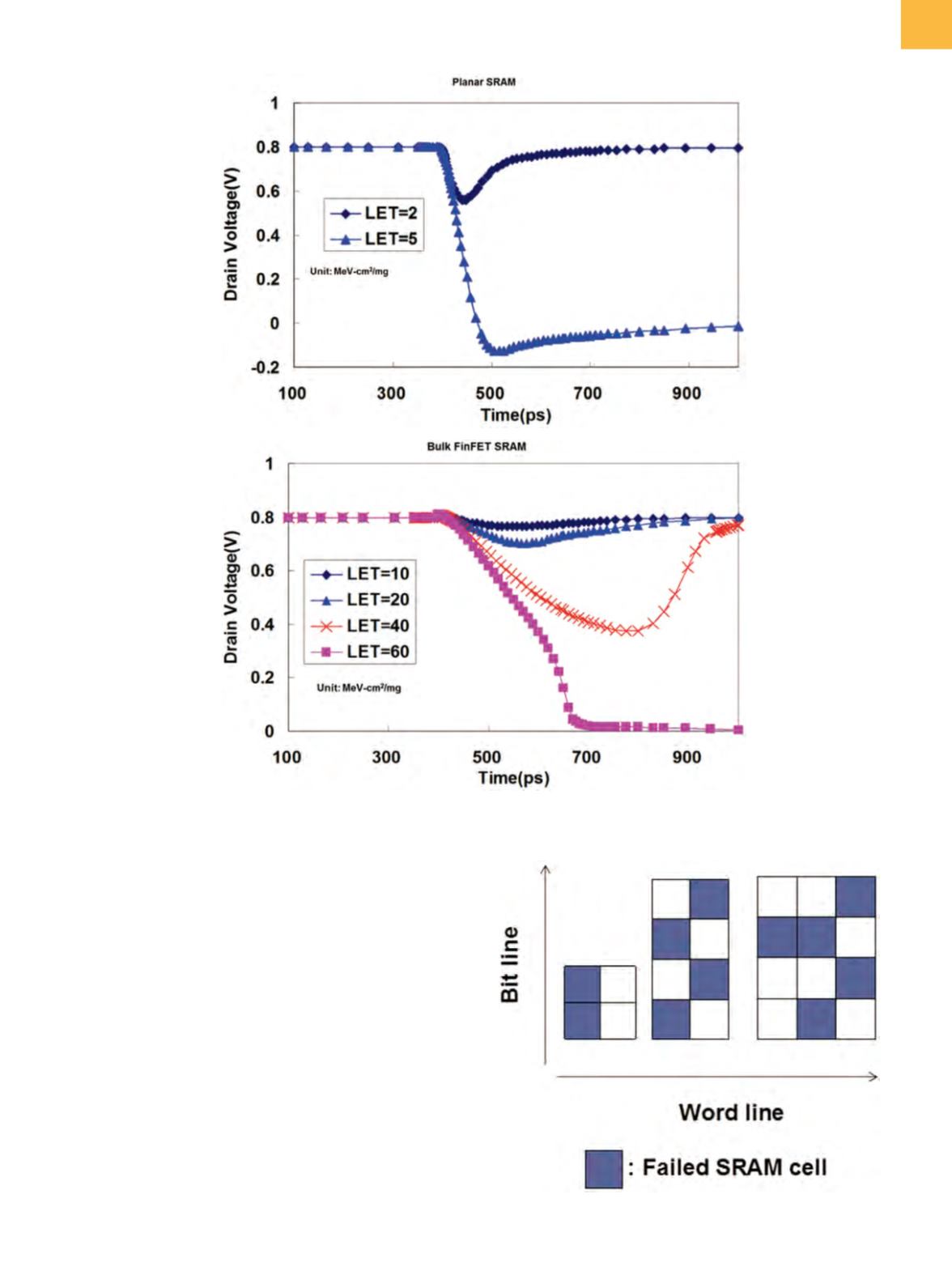

MULTICELL ERRORS

Thus far, only single-bit errors have been considered

for all particle sources. In reality, for high-energy neutrons

in particular, the range of errors introduced is larger than

this, and it is common to observe multiple bits (multicell

upsets, or MCUs) being simultaneously upset by a fast

neutron strike. Figure 8 shows examples of the MCU bit

map in a SRAMarray. As Fig. 3(b) shows, themagnitude of

MCU events has decreased in tandemwith SBU events as

silicon technology has progressed, with FinFETs showing

a similarly large reduction compared to planar devices

Fig. 7

Drain voltage variation with different LETs for (a) planar and (b) bulk FinFET SRAMs when the ion track does not cross the

drain

(a)

(b)

Fig. 8

Examples for MCU bit maps in a memory array