edfas.org

edfas.org

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 18 NO. 2

16

SOFT-ERROR SUSCEPTIBILITY OF FinFET SRAMs

Anthony S. Oates and Yi-Pin Fang, TSMC Ltd., Hsinchu, Taiwan

aoates@tsmc.comEDFAAO (2016) 2:16-27

1537-0755/$19.00 ©ASM International

®

INTRODUCTION

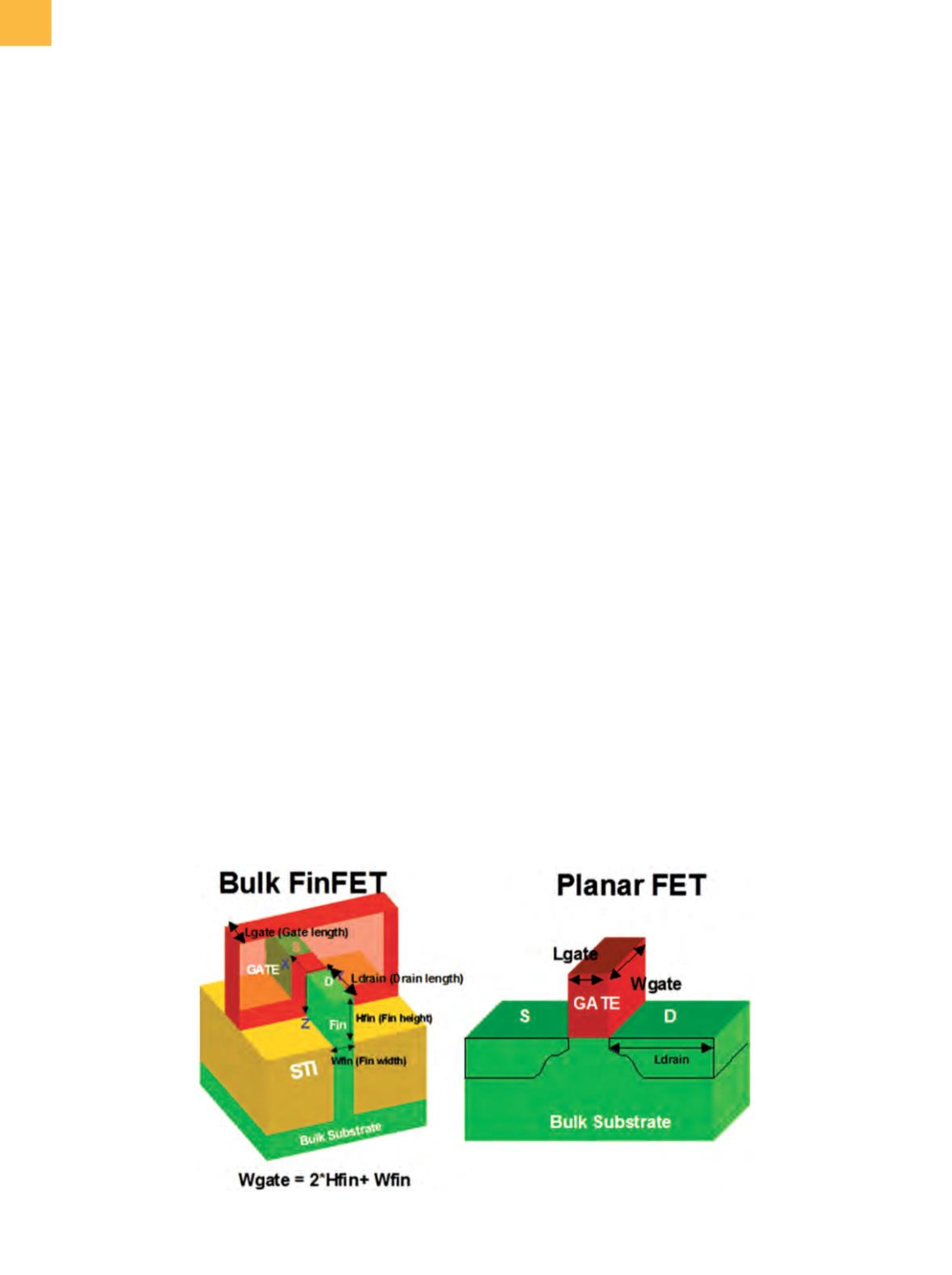

For technology scaling beyond 20 nm, FinFET transis-

tors will replace the conventional planar geometry. The

driving force for the introduction of FinFET architecture

is the superior immunity to short-channel effects and the

reduction of the effects of process variation on device

performance exhibited by the FinFET.

[1-4]

Figure 1 shows

a comparison of architectures of the planar FET and the

FinFET. One of the major concerns with the introduc-

tion of a new transistor architecture is ensuring that the

transistor maintains the high level of reliability required

for silicon circuits. Fortunately, in terms of reliability, the

transition to FinFETs has been smooth; FinFETs do not

introduce new reliability issues beyond those with which

we are familiar.

[4]

One of the most important reliability concerns for

silicon circuits is soft errors in SRAM circuits, which

involves electrical upsets generated by the interaction of

energetic atomic and subatomic particles with the silicon

substrate material. SRAMs are particularly sensitive to

radiation-induced soft errors due to the relatively low

amount of charge at the storage nodes. Errors are gener-

ated by the impact of alpha particles emitted from trace

amounts of uranium in solder and packagingmaterials of

the circuit, andbyneutrons that originate in the cosmic ray

shower in the Earth’s atmosphere. Alpha particles gener-

ate charge in the silicon substrate as they lose energy.

[5]

Neutrons, because they are electrically neutral, induce

errors when they collide with the silicon atoms of the

substrate, leading to the generation of charged secondary

ions. These ions generate charge as theymove through the

silicon.

[6]

There is a secondmechanismwhereby neutrons

induce errors: Cosmic ray neutrons have a wide energy

range (unlike alpha particles emitted frompackagemate-

rials), and low-energy (slow) neutrons may be captured

by naturally occurring B

10

atoms close to the surface of

the silicon substrate.

[7]

The decay of the B

10

resulting from

the neutron capture produces an energetic alpha particle

together with a lithium ion, both of which can gener-

ate charge in the silicon. For the most advanced silicon

process technologies, B

10

is commonly incorporated in

the contact regions of transistors due to the use of B

2

H

6

as

a carrier gas during tungsten contact deposition.

[8,9]

Soft

errorsmay also be generated by cosmic raymuons, which

are actually more abundant in the cosmic background

radiation than neutrons. However, the authors’ recent

work

[10]

indicates that errors due to muons are negligible

compared to alpha particles and neutrons, and somuon-

induced errors will not be discussed here.

Fig. 1

3-D schematic of a bulk FinFET compared with a planar FET