edfas.org

edfas.org

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 18 NO. 2

22

for both types of error. However, the probability of MCU

events shows a dependence on the technology node,

implying a dependence on the details of the processing

sequence because the SRAM design is similar in all cases.

While single-bit errors are readily corrected at the system/

circuit level using a variety of techniques that are com-

monly known as error-correction codes, these techniques

cannot be used to correct MCU events, and so the latter

tend to dominate the soft-error reliability of SRAMs.

The MCU events are caused by two mechanisms,

leaving aside the possibility of multicell errors caused by

a single direct ion strike. First is bipolar amplification of

charge collection caused by the turn-on of the parasitic

bipolar transistor formed by the source/bulk/drain of the

MOSFET. Positive charge accumulation in the silicon tub

region of the transistor is responsible for the turn-on of

the parasitic bipolar transistor. A secondmechanism that

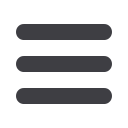

Fig. 9

Schematic 2-D top view for the inverter structure in a

SRAM. The ion is normally incident to the silicon surface

with a relative distance

D

x

(or

D

y

) away from the edge

of the drain.

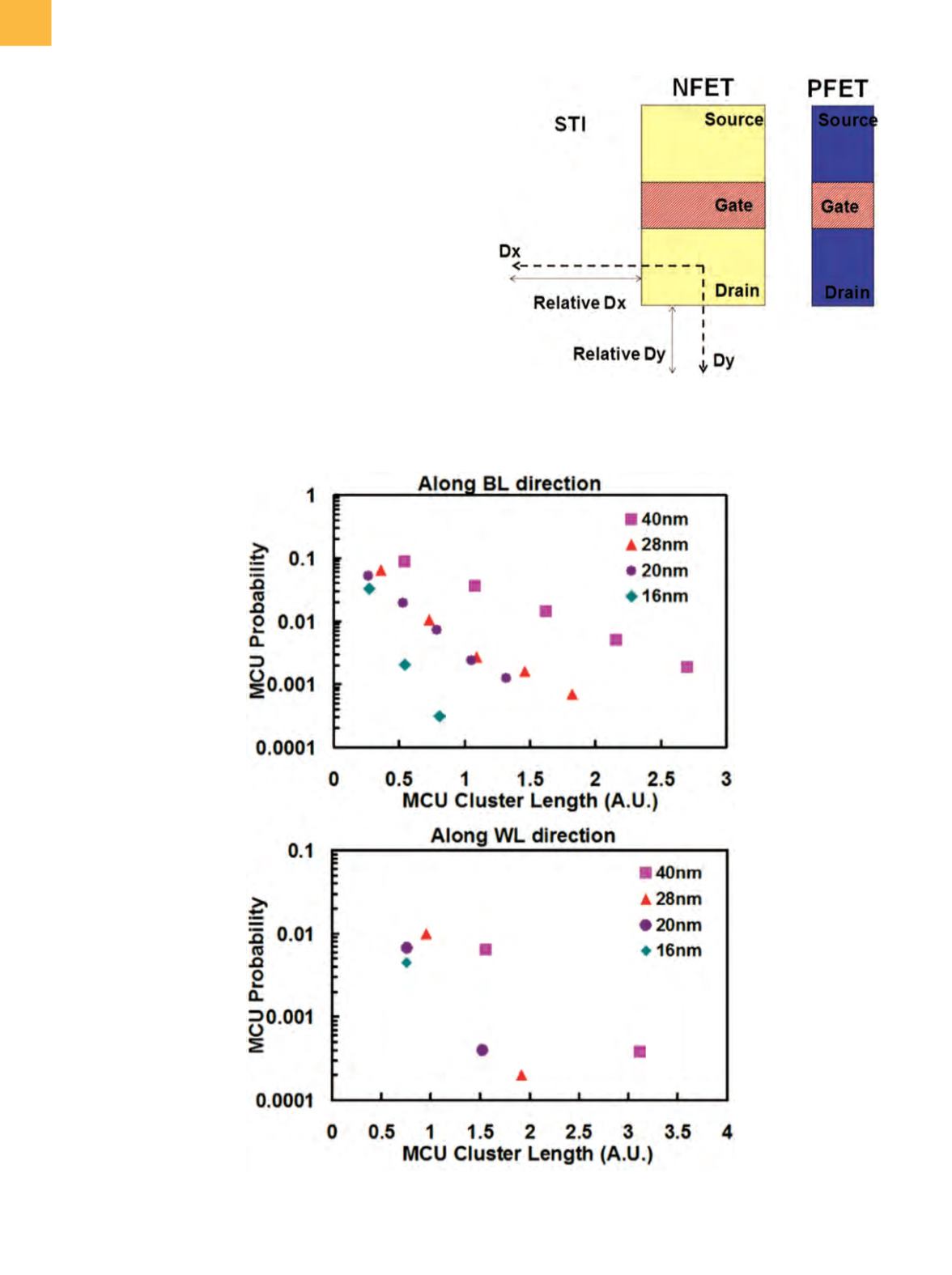

Fig. 10

Measured neutron-induced MCU cluster length distributions along the (a)

BL

direction and (b)

WL

direction for 40, 28, and

20 nm planar SRAMs and a 16 nm FinFET SRAM. The unit of the MCU cluster length has been scaled by a constant.

(a)

(b)