edfas.org

edfas.org

19

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 18 NO. 2

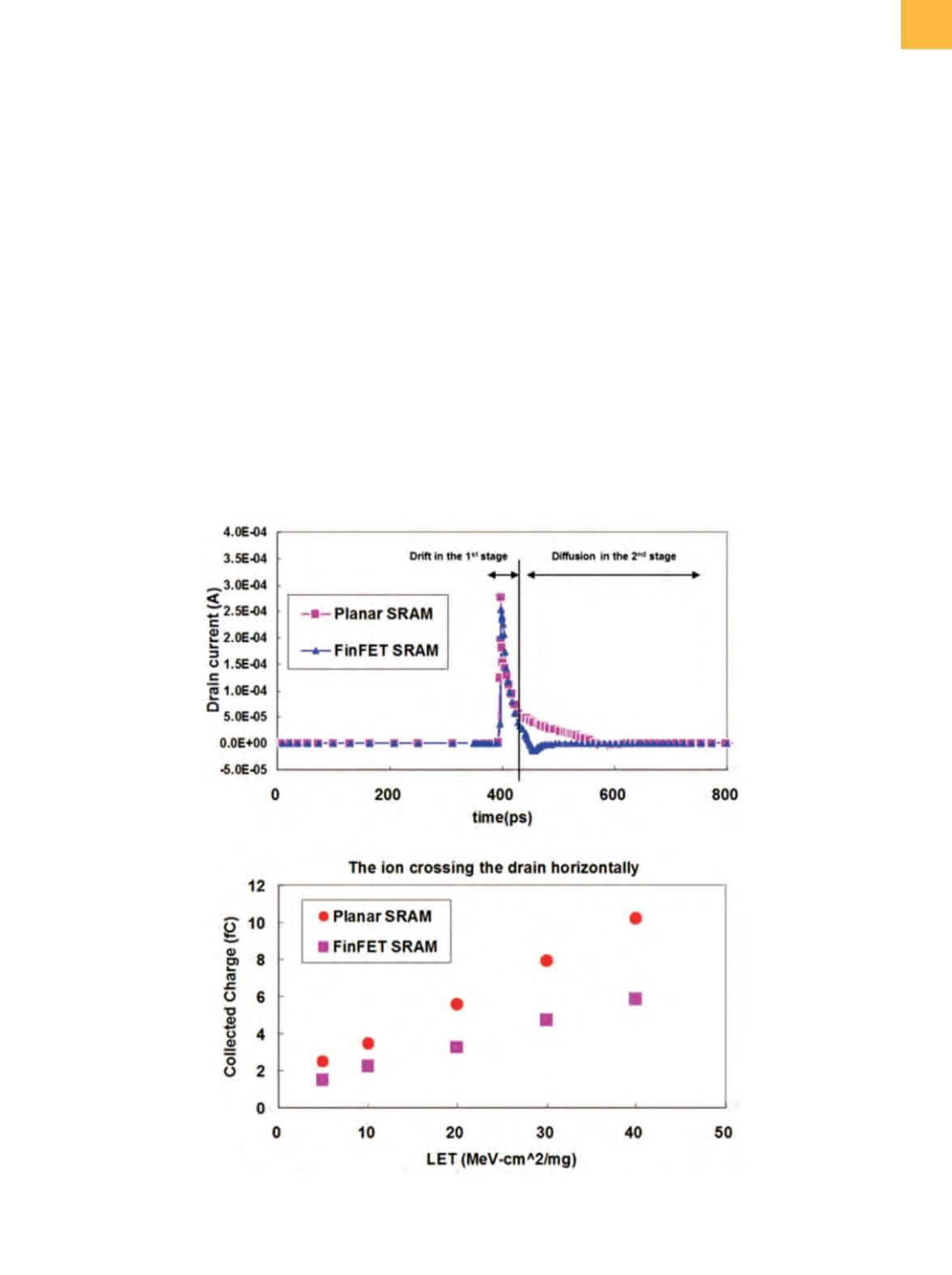

Fig. 5

(a) Comparison for drain current transients of planar and FinFET SRAMs when an ion of 30 MeV-cm

2

/mg strikes horizontally

through the drain. (b)

Q

coll

of planar and FinFET SRAMs from the horizontal track crossing the drain with different LETs

available for charge collection is smaller than that for

planar devices, so a smaller amount of deposited charges

canbe expected todiffuse to the FinFETdrain. Simulations

of the transistor response to energetic ion strikes were

performed using the Synopsys Sentaurus 3-D tool. Details

of the simulation procedure are described in Ref 14.

Two ion-strike conditions are considered in these simu-

lations. The first involves ion strikes to the drainwhere the

ion track either crosses the drain along its length in the

center of the drain body or occurs at normal incidence

fromthe top and vertically crosses the drain. In the second

condition, the ion strikes the bulk substrate at a distance

approximately 0.5 μm under the drain, and the ion track

does not cross the drain. The collected charge,

Q

coll

, of the

drain node of the

n

-FET is then calculated by integrating

the transient current over this time interval. An upset of

the data stored in the SRAM cell occurs when the

Q

coll

is

collected over a threshold value,

Q

crit

, which results in a

flip of the stored data. Figure 4 shows the drain voltage as

a function of time for both bulk FinFET and planar SRAMs

when the ion track crosses the drain along its length at

a time of 400 ps in the simulation. In this instance, an

incident ion linear energy transfer (LET) = 30MeV-cm

2

/mg

is chosen. In both cases, the drain voltage falls after the

ion strikes, while the voltage of the gate increases.

Q

crit

is

obtained by integrating the drain transient current that

results from a collision of an energetic particle with the

silicon substrate over the time at which the falling drain

voltage crosses the increasing gate voltage. The simulated

Q

crit

of the FinFET SRAM is 1.53 fC, and that of the planar

SRAM is 1.46 fC. The similarity of the

Q

crit

values of FinFET

and planar SRAMs is reasonable because the effective

W

gate

,

L

gate

, and

T

ox

, as well as the operation voltage, are

identical.

Figure 5(a) shows the comparison of the drain current

transients arising froma horizontal ion strike through the

n

-FET drain with an LET of 30 MeV for the bulk FinFET and

planar SRAMs. The time-dependent drain current pulses of

(a)

(b)