# ELECTRONIC DEVICE FAILURE ANALYSIS™

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

## ■ ■ ■ 2016 WINNERS PAGE 64

**4**

FAILURE ANALYSIS OF DC/DC

CONVERTERS: A CASE STUDY

**12**

NANOSCALE CAPACITANCE AND

CAPACITANCE-VOLTAGE CURVES FOR

ADVANCED CHARACTERIZATION OF

ELECTRICAL PROPERTIES OF SILICON

AND GaN STRUCTURES USING

SCANNING MICROWAVE IMPEDANCE

MICROSCOPY (sMIM)

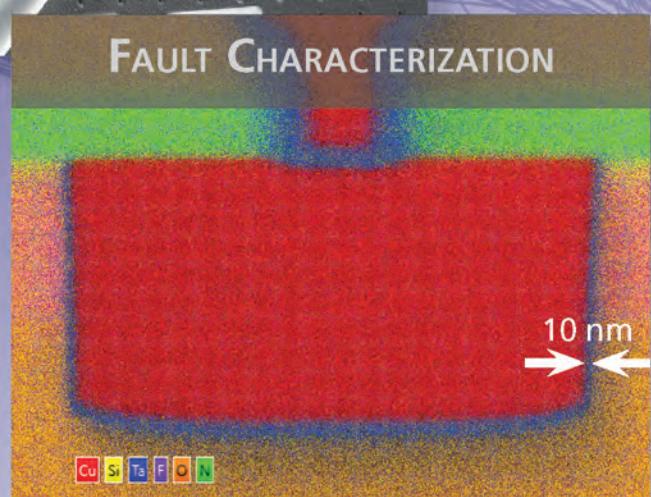

**22**

PRODUCT CIRCUIT VALIDATION AND

FAILURE DEBUG: A SEMICONDUCTOR

FOUNDRY CAN HELP

**36**

PLASMA FIB DEPROCESSING OF

INTEGRATED CIRCUITS FROM

THE BACKSIDE

# UNLOCK THE ANSWERS TO YOUR FAILURE ANALYSIS QUESTIONS WITH

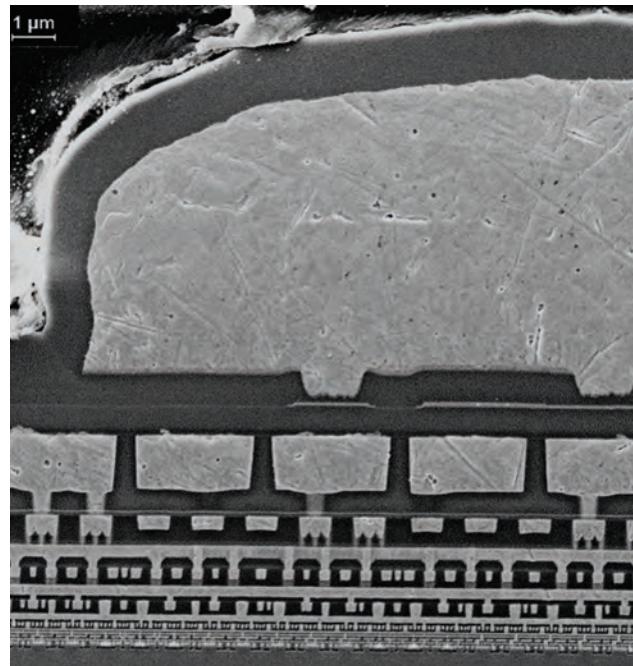

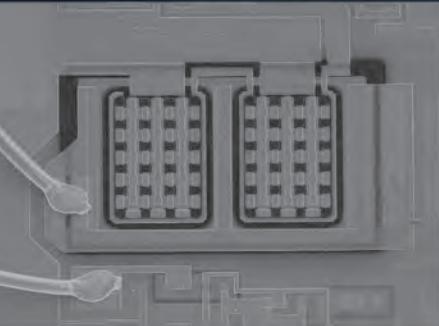

SEM Image of Semiconductor Device

Passive Voltage Contrast (PVC)

image of semiconductor device

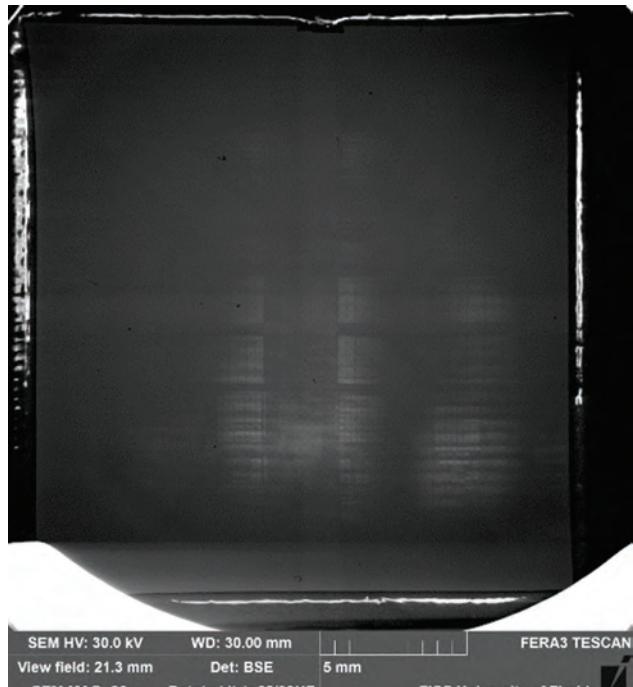

Backscatter Electron (BSE)

image of Wire Bond Cross Section

Electron Beam Induced Current (EBIC)

Image of Semiconductor Device

SMART

FLEXIBLE

POWERFUL

SEM

## Questions about...

- *Fatigue?*

- *Delamination?*

- *Corrosion?*

- *Layer Integrity?*

- *Fracture?*

- *Interfaces?*

Come see how JEOL high resolution, analytical Scanning Electron Microscopes and precision Cross Section Polishers help you get answers.

Visit [jeolusa.com/jeolfa](http://jeolusa.com/jeolfa)

**JEOL**

Solutions for Innovation

[salesinfo@jeol.com](mailto:salesinfo@jeol.com)

# ELECTRONIC DEVICE FAILURE ANALYSIS™

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

## ■ ■ ■ 2016 WINNERS PAGE 64

4

FAILURE ANALYSIS OF DC/DC

CONVERTERS: A CASE STUDY

12

NANOSCALE CAPACITANCE AND

CAPACITANCE-VOLTAGE CURVES FOR

ADVANCED CHARACTERIZATION OF

ELECTRICAL PROPERTIES OF SILICON

AND GaN STRUCTURES USING

SCANNING MICROWAVE IMPEDANCE

MICROSCOPY (sMIM)

22

PRODUCT CIRCUIT VALIDATION AND

FAILURE DEBUG: A SEMICONDUCTOR

FOUNDRY CAN HELP

36

PLASMA FIB DEPROCESSING OF

INTEGRATED CIRCUITS FROM

THE BACKSIDE

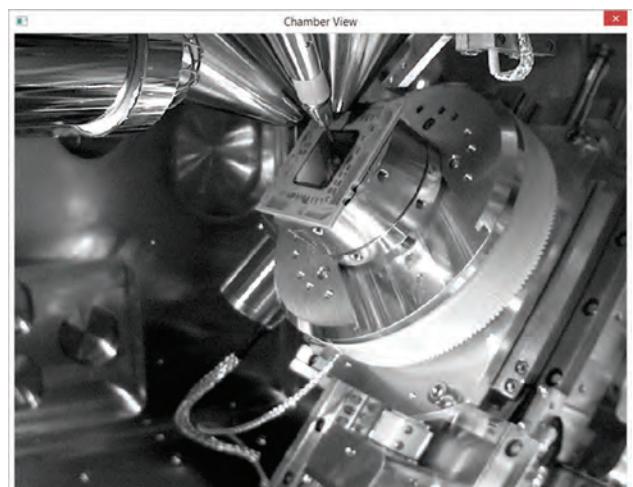

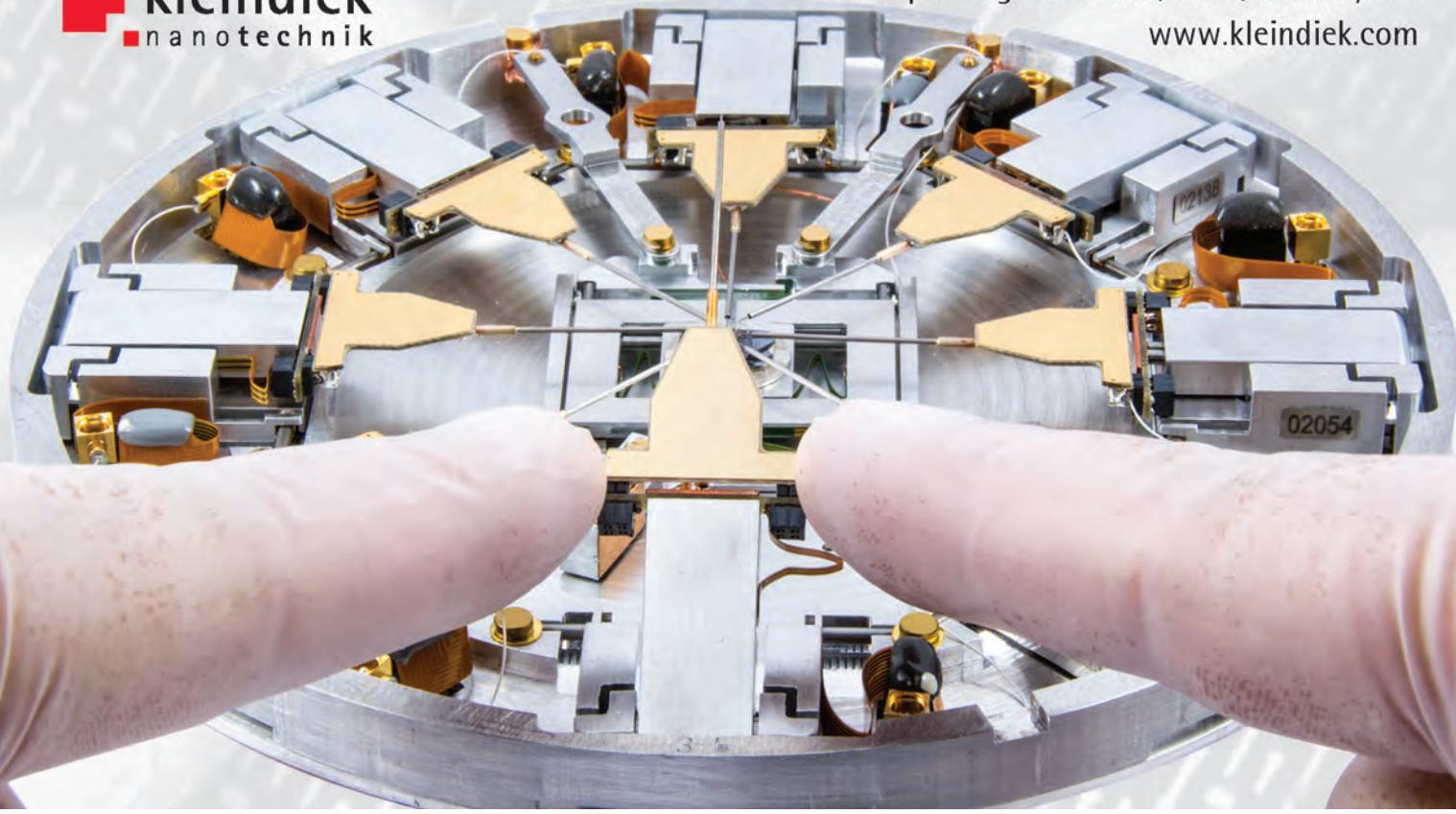

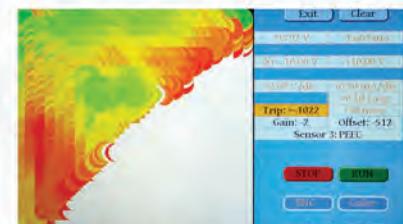

# ASAP-1® IPS

## Interactive Preparation System

- Realtime Video Monitor with System Parameters

- Huge Cavity Size Range -  $<0.25\text{mm}^2$  to  $>1,600\text{mm}^2$

- Automatic Endpoint option

- Full 5-Axis systems available

- **Open System Design** allows for fixturing all types and size of part – from surface-mount components, up to Motherboards and Wafers

- Touch-screen control with physical Joystick and Controls – **Best of Both Worlds**

- Meet Current SIL/LVP Requirements (demonstrated  $50\mu\text{m}$  RST  $+-2\mu\text{m}$  on Flip Chip), and Single Digit RST

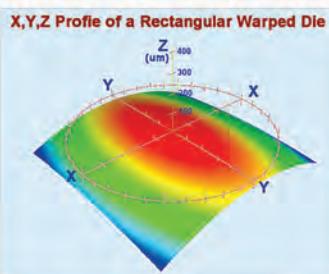

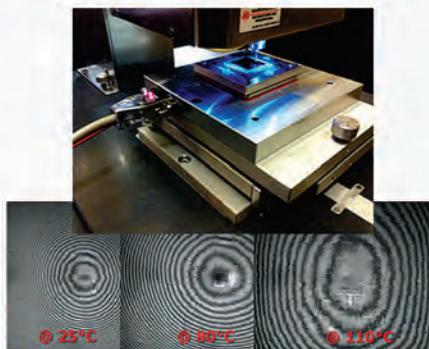

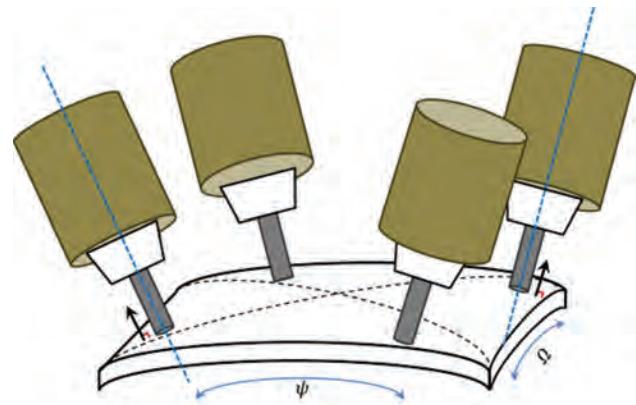

### MEET 3D & CURVED/WARPED SURFACE CHALLENGES WITH ADVANCED TECHNIQUES

#### Curvature Compensation

- Auto-Curve and Auto-tilt Setup

- Independent X & Y Axes

- Convex & Concave Surfaces

#### Thermal Relaxation

- Safe and Reliable method to turn complex 3D scenarios into simpler 2D ones

- Reduces dynamic flex of substrate during preparation

- In-situ Hotplate Mode for sample mounting

#### All Package Types & Sizes

- Parts can be decapped, thinned & polished in as little as 45 minutes

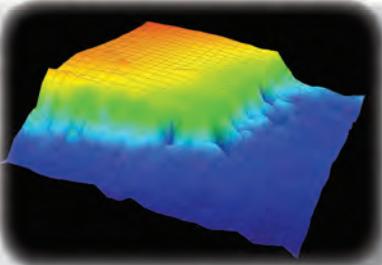

#### F-Series Wafer Thickness Measurement System

- Multiple or single-point measurements

- Both 2D and 3D data generated

- Provides Information for achieving final uniformity

**ULTRA TEC**

MANUFACTURING, INC.

Toll Free (US) 1-877-542-0609

Tel: 1-714-542-0608 Fax: 1-714-542-0627

e-mail: [info@ultratecusa.com](mailto:info@ultratecusa.com)

[www.ultratecusa.com](http://www.ultratecusa.com)

# ELECTRONIC DEVICE FAILURE ANALYSIS™

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

4

12

## 4 Failure Analysis of DC/DC Converters: A Case Study

Jérémie Dhennin

DC/DC converters are widely used in electronic applications, especially in the aerospace industry. This case study discusses the challenges of adapting sample-preparation techniques for defect localization as well as understanding the root cause of the failure.

## 12 Nanoscale Capacitance and Capacitance-Voltage Curves for Advanced Characterization of Electrical Properties of Silicon and GaN Structures Using Scanning Microwave Impedance Microscopy (sMIM)

Oskar Amster, Stuart Friedman, Yongliang Yang, and Fred Stanke

Scanning microwave impedance microscopy provides the capability to directly probe a sample's permittivity and conductivity at submicron geometries, providing valuable nanoscale information about semiconductor devices, processes, and defects.

## 22 Product Circuit Validation and Failure Debug: A Semiconductor Foundry Can Help

Edy Susanto, S.H. Goh, Edmund C. Manlangit, and Jeffrey Lam

Faster time-to-production of a new product is the common goal of design houses and foundries. This article demonstrates how foundries can contribute through postsilicon validation, which allows design houses to focus on more complicated issues.

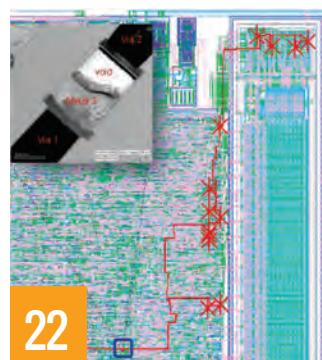

22

36

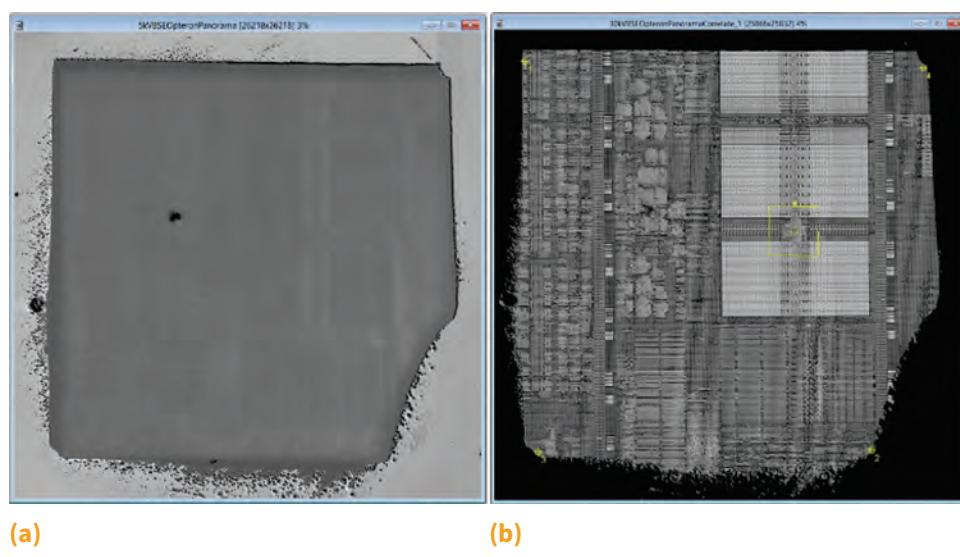

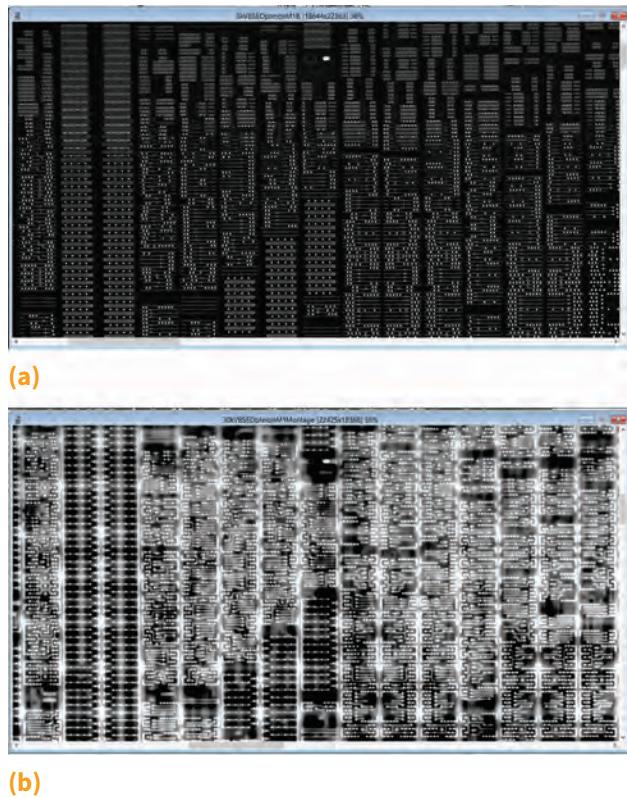

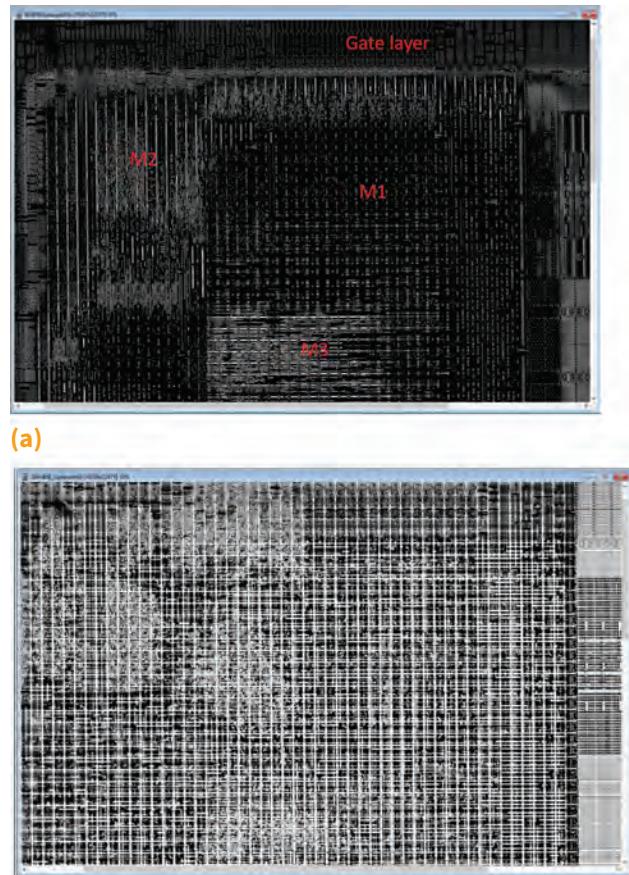

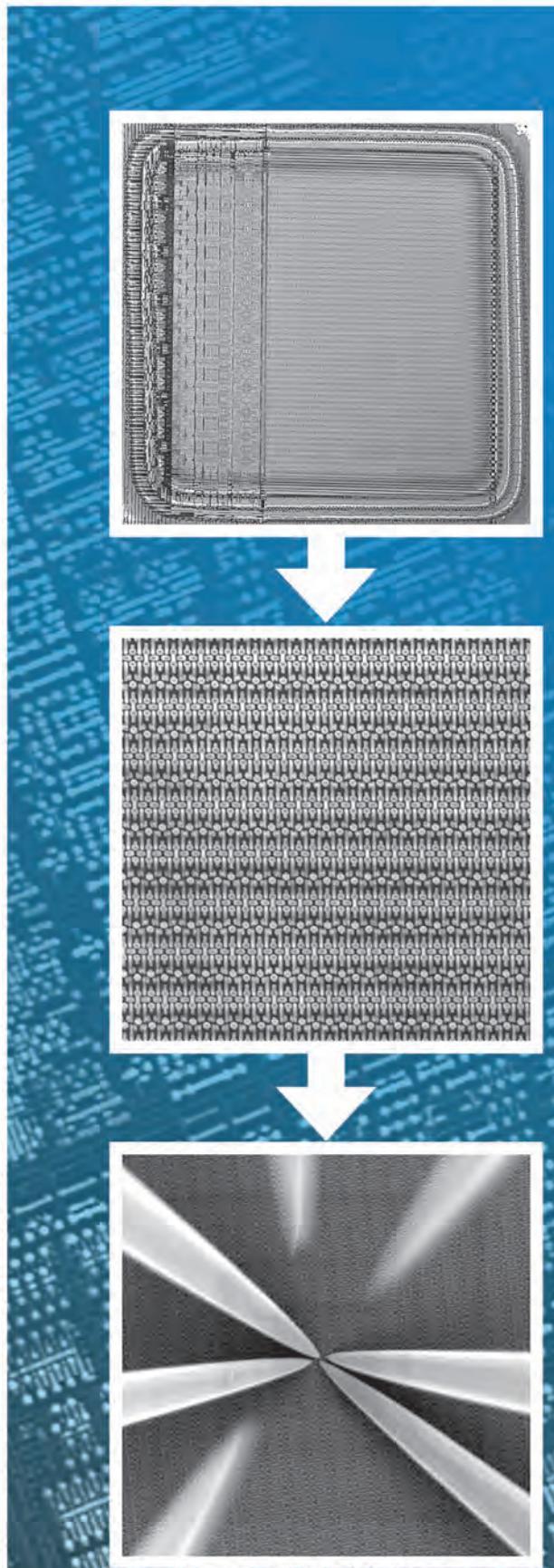

## 36 Plasma FIB Deprocessing of Integrated Circuits from the Backside

E.L. Principe, Navid Asadizanjani, Domenic Forte, Mark Tehraniipoor, Robert Chivas, Michael DiBattista, and Scott Silverman

Deprocessing of ICs is often the final step for defect validation in FA cases with limited fault-isolation information. A workflow for deprocessing from the backside uses a combination of automated adaptive backside ultrathinning and large-area plasma FIB delayering.

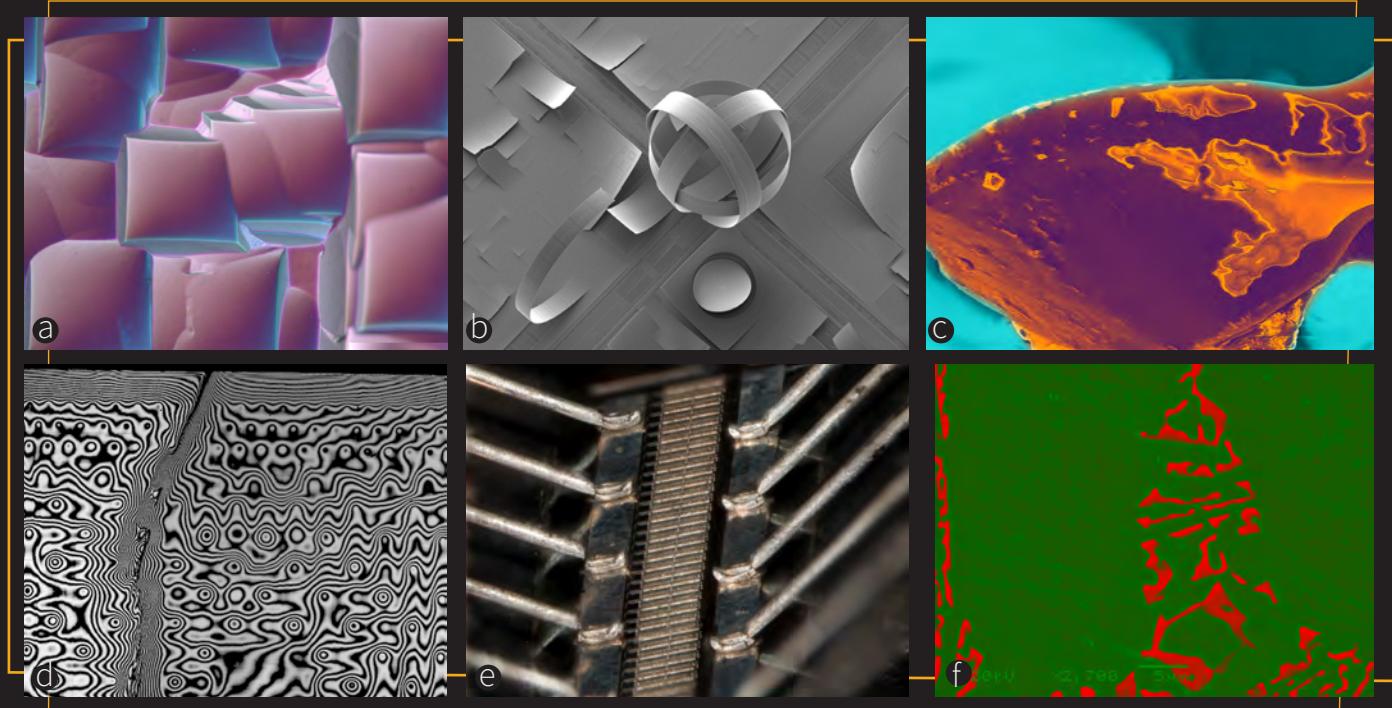

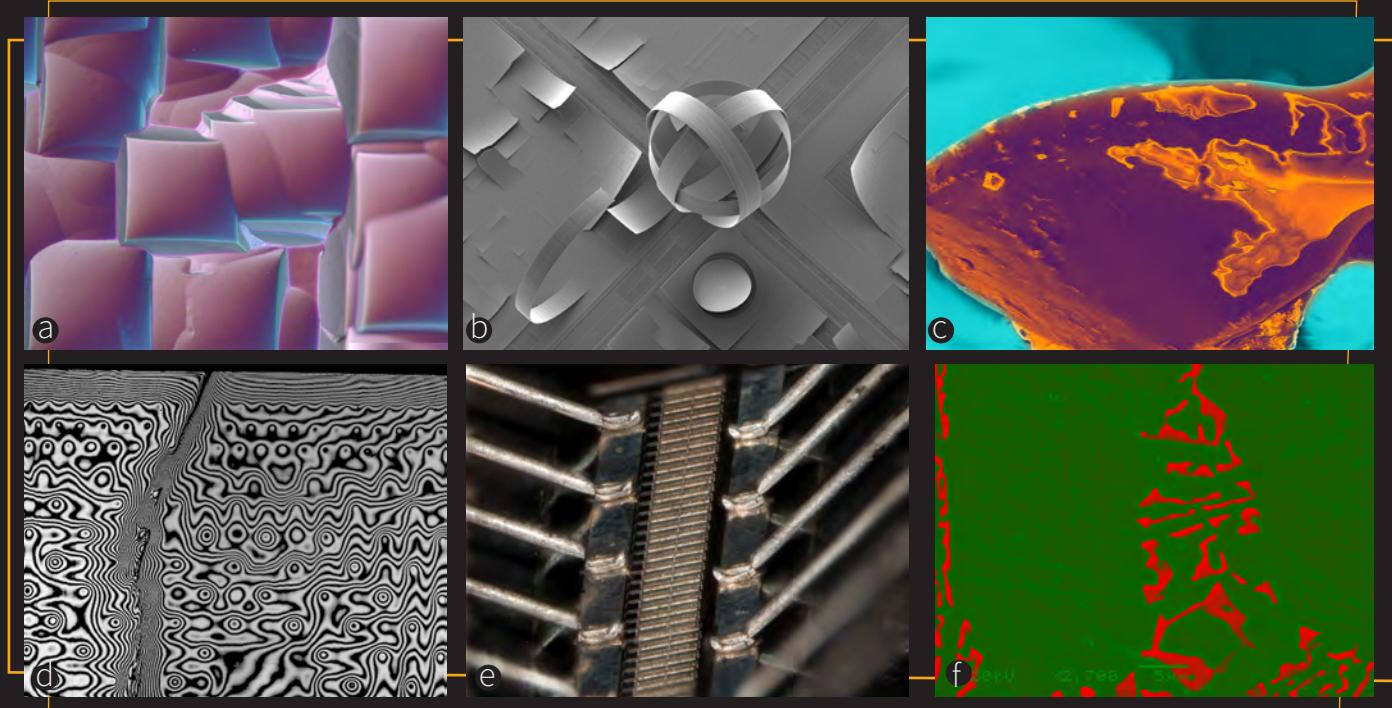

## ABOUT THE COVER

See page 64 for a description of the contest winners' collage on the cover.

## Author Guidelines

Author guidelines and a sample article are available at [edfas.org](http://edfas.org). Potential authors should consult the guidelines for useful information prior to manuscript preparation.

For the digital edition, log in to [edfas.org](http://edfas.org), click on the "News/Magazines" tab, and select "EDFA Magazine."

## DEPARTMENTS

**46 SPECIAL! ISTFA 2017 SHOW LISTING**

**64 ADVERTISERS' INDEX**

**34 SAVE THE DATE**

**54 DIRECTORY OF FA PROVIDERS** *Rose Ring*

**2 EDITORIAL** *Felix Beaudoin*

**62 GUEST COLUMNISTS** *Rao Desineni and Yan Pan*

**44 INTERNET RESOURCES** *Rose Ring*

**50 INVENTOR'S CORNER** *Dave Vallett*

**60 LITERATURE REVIEW** *Mike Bruce*

**52 PRODUCT NEWS** *Larry Wagner*

**56 TRAINING CALENDAR** *Rose Ring*

**PURPOSE:** To provide a technical condensation of information of interest to electronic device failure analysis technicians, engineers, and managers.

**Felix Beaudoin**

Editor/GLOBALFOUNDRIES; [felix.beaudoin@globalfoundries.com](mailto:felix.beaudoin@globalfoundries.com)

**Scott D. Henry**

Publisher

**Mary Anne Fleming**

Manager, Technical Journals

**Kelly Sukol**

Production Supervisor

**Liz Marquard**

Managing Editor

**ASSOCIATE EDITORS**

**Nicholas Antoniou**

Revera, Inc.

**Michael R. Bruce**

Consultant

**David L. Burgess**

Accelerated Analysis

**Jiann Min Chin**

Advanced Micro Devices Singapore

**Edward I. Cole, Jr.**

Sandia National Labs

**James J. Demarest**

IBM

**Szu Huat Goh**

GLOBALFOUNDRIES Singapore

**Ted Kolasa**

Orbital ATK

**Andreas Meyer**

GLOBALFOUNDRIES

**Philippe H.G. Perdu**

CNES France

**Rose M. Ring**

Qorvo, Inc.

**Paiboon Tangyunyong**

Sandia National Labs

**David P. Vallett**

PeakSource Analytical, LLC

**E. Jan Vardaman**

TechSearch International, Inc.

**Martin Versen**

University of Applied Sciences Rosenheim, Germany

**Lawrence C. Wagner**

LWSN Consulting Inc.

**GRAPHIC DESIGN**

Janet Nejedlik - [designbyj.com](http://designbyj.com)

**PRESS RELEASE SUBMISSIONS**

**[magazines@asminternational.org](mailto:magazines@asminternational.org)**

*Electronic Device Failure Analysis™ (ISSN 1537-0755) is published quarterly by ASM International®, 9639 Kinsman Road, Materials Park, OH 44073; tel: 800.336.5152; website: [edfas.org](http://edfas.org). Copyright© 2017 by ASM International. Receive *Electronic Device Failure Analysis* as part of your EDFAS membership of \$88 U.S. per year. Non-member subscription rate is \$135 U.S. per year.*

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by ASM International for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$19 per article is paid directly to CCC, 222 Rosewood Drive, Danvers, MA 01923, USA.

*Electronic Device Failure Analysis* is indexed or abstracted by Compendex, EBSCO, Gale, and ProQuest.

# EDITORIAL

## EDFAS SUCCESS THROUGH VOLUNTEERS!

Felix Beaudoin, Editor

GLOBALFOUNDRIES

[felix.beaudoin@globalfoundries.com](mailto:felix.beaudoin@globalfoundries.com)

“Striving for 100% Success Rate” is the theme of the 2017 International Symposium for Testing and Failure Analysis (ISTFA). If you attend the conference, you will certainly find the keys to success by joining the many planned technical sessions, users’ groups, panel discussion, keynote presentation, and by exchanging with your peers. This year I have the privilege to act as the Technical Program Chair, and I assure you the conference will deliver on the technical quality, thanks to the dedication of all the volunteers on the ISTFA Organizing Committee. To the 100+ technical chairs, co-chairs, and reviewers who spent endless hours diligently mentoring oral and poster manuscripts, THANK YOU!

Success can be defined and measured in several ways. The panel discussion on the conference theme will surely debate questions such as: What does 100% success rate really mean to your organization? How best to overcome challenges in order to achieve success? As an individual contributor, I have the firm belief that success in our field of electronic device failure analysis can only be achieved by developing broad interdisciplinary scientific and technological knowledge. Peer mentoring, technical conferences, tutorials, short courses, and publications are all sources of information that are part of the EDFAS Society’s mission to foster education and communication in the failure analysis community, which is, of course, powered by volunteers.

In particular, *EDFA* magazine relies on its volunteer Associate Editors, listed on page 2, to recruit and mentor technical contributions, write the various informative departments, and seek out guest editorials and columnists from experts worldwide. I would like to recognize James J. Demarest, who will be retiring from the *EDFA* Editorial Board. His main motive in stepping aside is to make way for new volunteers, fostering the growth of the magazine through fresh opportunities to serve. His expertise will be deeply missed.

*EDFA* magazine, and more generally our EDFAS Society, can only thrive with the help of volunteers like you. Please consider contributing technical articles to share your knowledge. New communication and social media tools now establish virtual content and help reach a broader audience who are dealing with failure of electronic devices in emerging application fields. We need help to create content for those new platforms. If you attend the conference, do not hesitate to stop me or any of the EDFAS Board members and Technical Session Chairs to introduce yourself and discuss your interests.

Ready to get involved? Please contact me or Sweta Pendyala, the Volunteer Committee Chair, at [sweta.pendyala@globalfoundries.com](mailto:sweta.pendyala@globalfoundries.com). EDFAS can be “Striving for 100% Success Rate” only with volunteers like you!!!

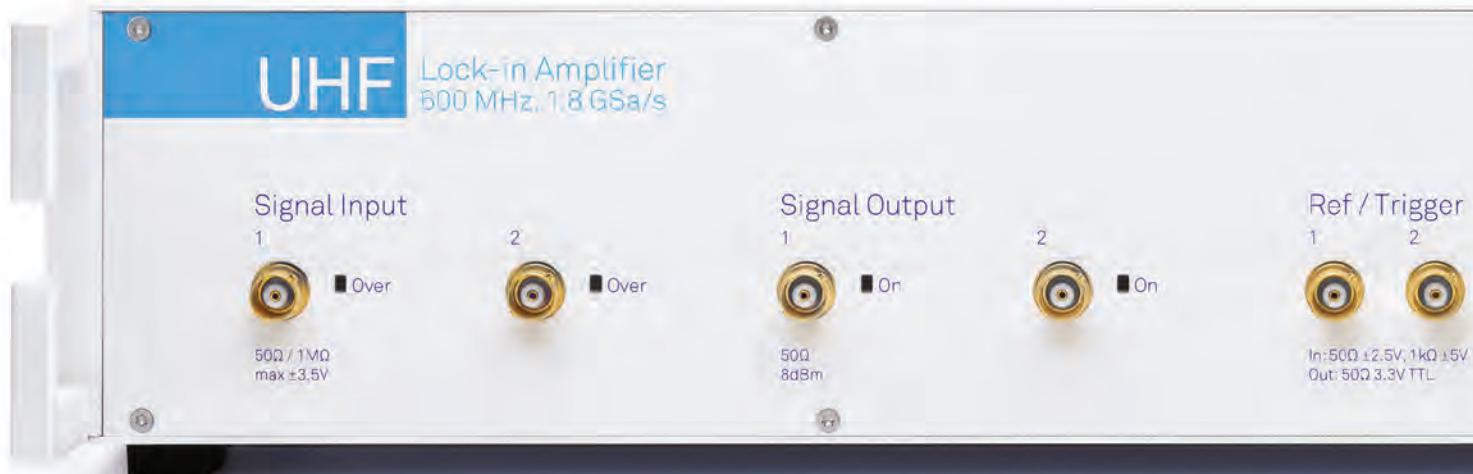

# Need higher resolution?

Use the Zurich Instruments UHFLI

to generate and analyze your

signal patterns up to 600 MHz

ISTFA/2017

booth #804

## The Zurich Instruments UHFLI

Lock-in amplifier measures amplitude and phase information with high signal-to-noise ratio and high precision

AWG generates any waveform on the outputs

Boxcar & Scope extract specific subsets from complex excitation patterns

Imaging module converts your measurements directly into images

APIs provide full control and integration through LabVIEW®, MATLAB®, C#, Phyton and .NET

Analog Interfacing integrates easily with your existing Failure Analysis equipment

Get in touch

[www.zhinst.com](http://www.zhinst.com)

[info@zhinst.com](mailto:info@zhinst.com)

Intl. +41 44 515 0410

USA +1 617 765 7263

Your Application. Measured.

Zurich

Instruments

# FAILURE ANALYSIS OF DC/DC CONVERTERS: A CASE STUDY

Jérémie Dhennin, ELEMCA

jeremie.dhennin@elemca.com

## INTRODUCTION

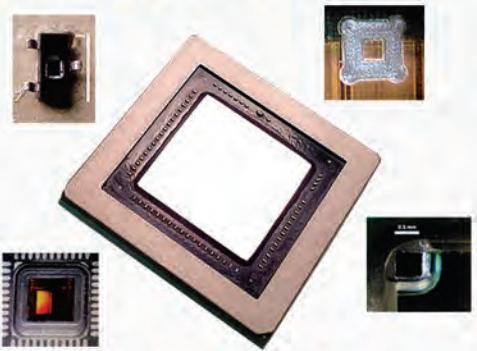

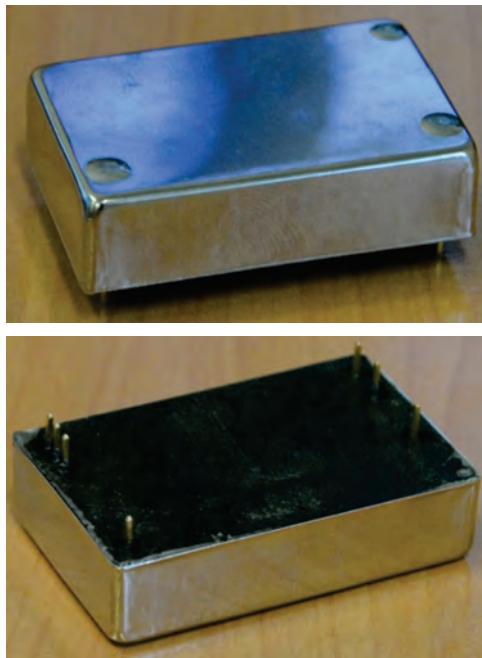

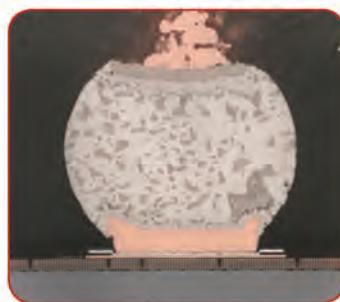

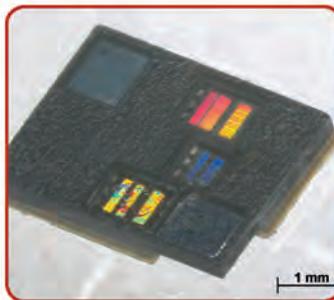

DC/DC converters are widely used in electronic applications and, in particular, in the aerospace industry. In this case study, a defective part was retrieved from an aircraft following an abnormal system behavior detected by the airline crew. The incriminated component is a DC/DC converter, which has a single 28 V input and two outputs, at 5 and 18 V.

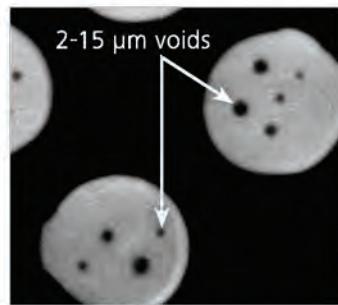

The main difficulty in the failure analysis of such a component is its integration. Two printed circuit board assemblies (PCBAs) are assembled in the same package and molded in a resin (Fig. 1). This layout induces additional challenges for the failure investigation, because 3-D techniques must be used to locate the defect.

As usual, the first step of the failure analysis process is to electrically test the component and determine the region that will be further analyzed in the next steps. Here, any local probing of the PCBAs is complicated by the

**Fig. 1** Photos of the DC/DC converter

presence of the overmolding resin. This obstacle makes the failure analysis difficult from the outset.

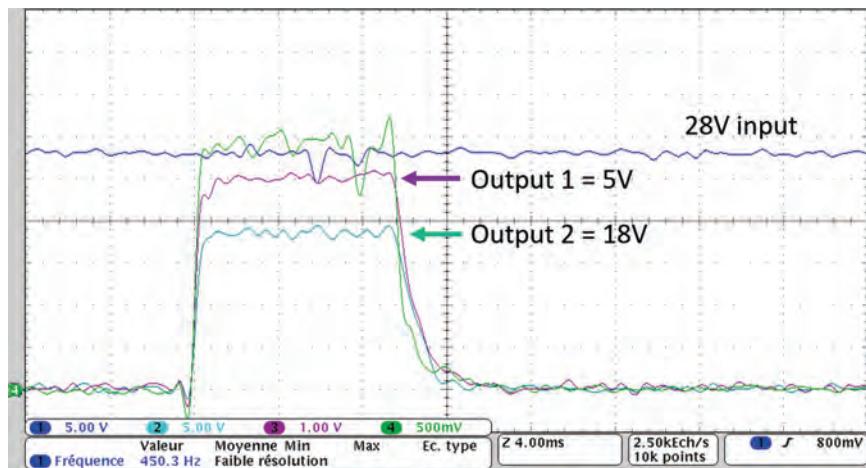

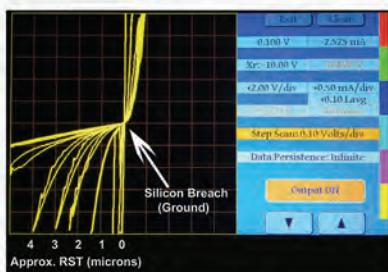

## DEFECT LOCALIZATION ELECTRICAL TESTING

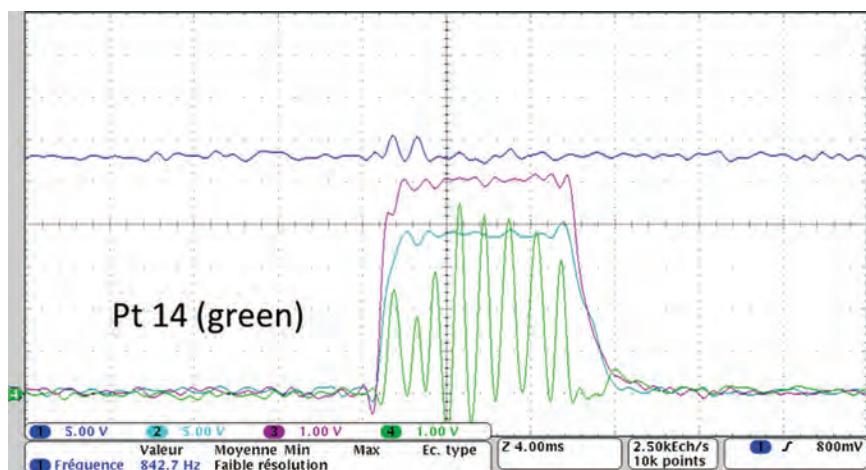

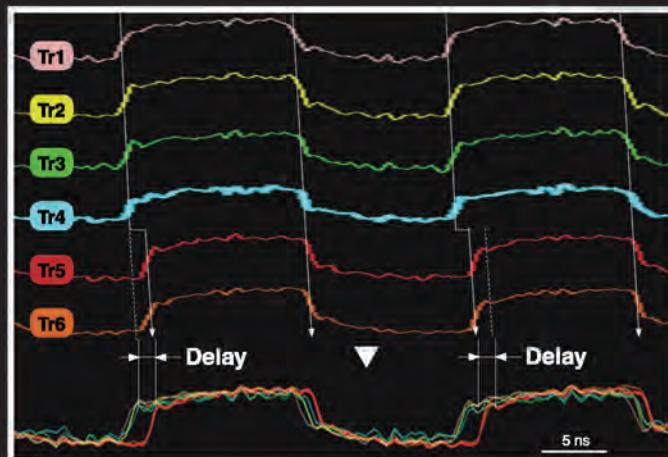

The observed failure mode is a bad converter startup. Indeed, the overvoltage/undervoltage protection section seems to be unduly activated. The outputs are correctly set by the component but are trimmed down to 0 V after a few milliseconds. An oscilloscope plot is presented in Fig. 2.

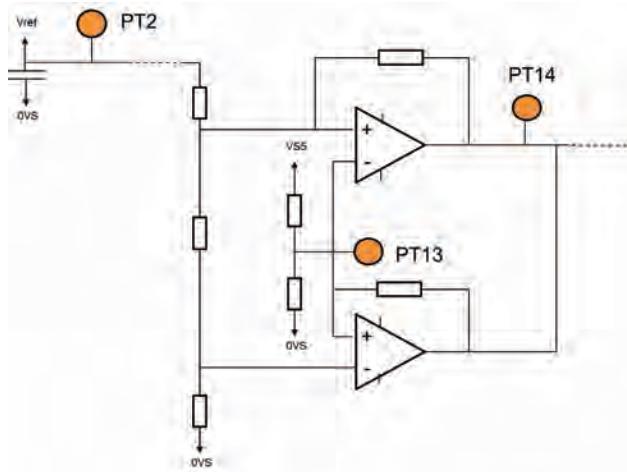

The resin was locally opened to access probing areas to investigate the overvoltage/undervoltage region. This function consists basically in a comparator system (Fig. 3).

## LOCAL PROBING

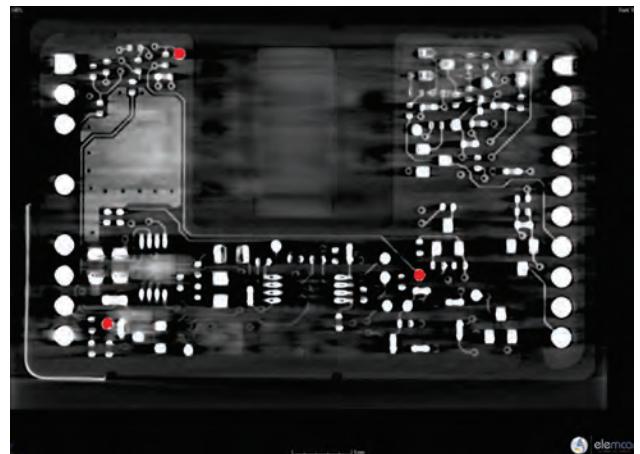

The probing areas were opened with a laser ablation system. To accurately locate the test points, x-ray computerized tomography (CT) of the entire converter was performed. It is important to obtain precise localization of the regions to be opened, because the functionality of the converter must be ensured. Indeed, approximately 1 mm backlash is used to place the PCBAs in the converter cap before molding. Consequently, the exact position of the components inside the converter is not known.

With x-ray CT, a virtual volume of the device was obtained. The latter has been superimposed with an optical image to correlate the internal structure of the PCBA with the external shape of the converter. The 40 µm scan resolution is accurate enough to determine the exact position of the regions to be opened. Figure 4 presents a virtual slice of the PCBA, obtained by x-ray CT, with the opening points identified in red.

Local probing shows that the input of the converter system is not defective, but the output exhibits large oscillations (Fig. 5).

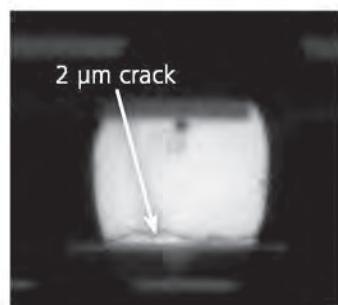

## X-RAY IMAGING

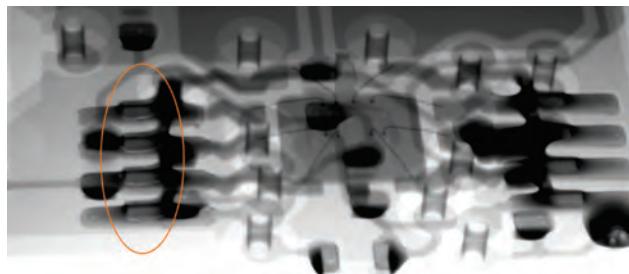

Focused x-ray imaging of the small-outline eight-pin (SO8) component (Fig. 6) confirmed that it is the defective

device. Cracks were detected on four pins located on the same side of the component.

Of course, this defect could have been seen from the beginning of the failure analysis process. X-ray imaging had been performed at the start, but it is almost impossible to

find the defect when one does not know where to look for it. Also, x-ray images are tricky to read, because the device is a superposition of two double-sided PCBAs.

The same defect was found on other nonfunctional DC/DC converters.

**Fig. 2** Oscilloscope plot of the input/output signals

**Fig. 3** Simplified design of the overvoltage/undervoltage protection function

**Fig. 4** Identification of the test points on a virtual slice obtained by x-ray CT

**Fig. 5** Local probing results (output of the comparator in green)

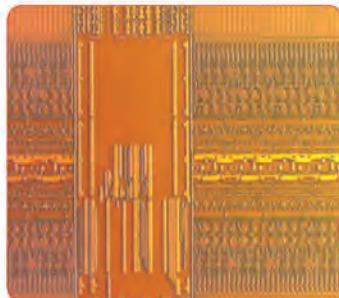

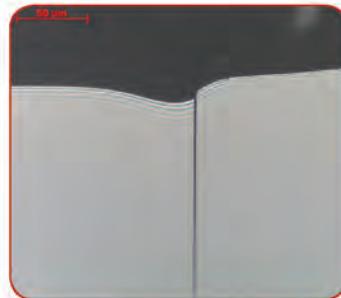

## DESTRUCTIVE ANALYSIS

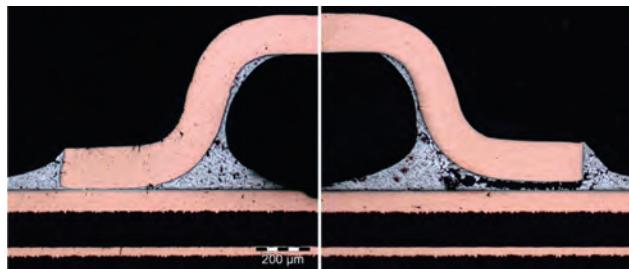

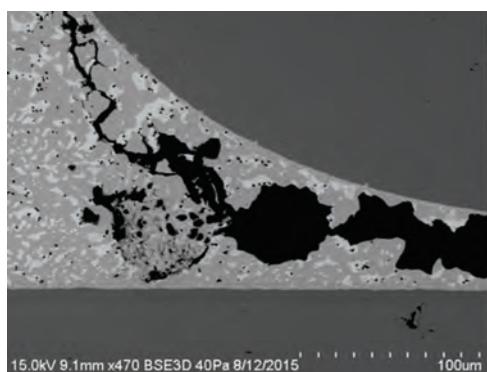

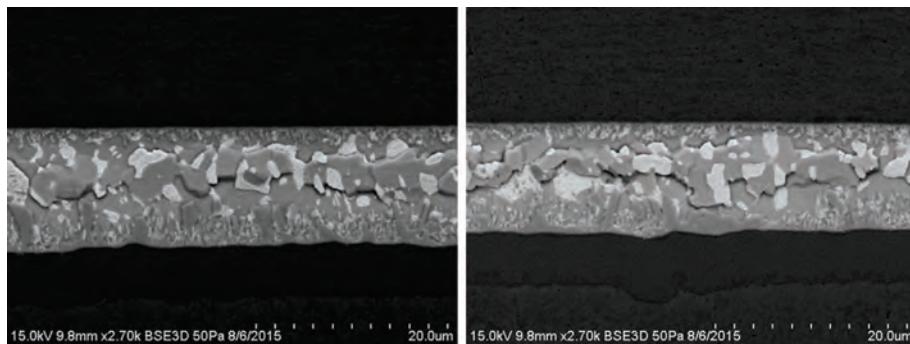

To inspect the solder material, a cross section was performed with optical (Fig. 7) and scanning electron microscopy (SEM) imaging (Fig. 8).

A crack was confirmed under one pin. The other side of the component was not affected. The solder material thickness between the pin and the pad was found to be very low.

The SEM observation showed that phase segregation has occurred. The intermetallic at the interfaces with the pin and the pad is continuous and seems correctly formed.

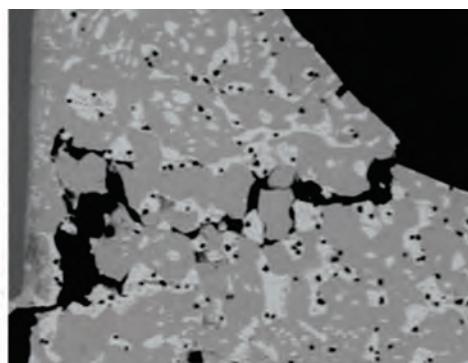

Other functional DC/DC converters were also studied to control the solder material. Recrystallization was found on many of them (Fig. 9). Recrystallization is an early stage of crack formation. The strain that is stored in the material is released by rearranging the atoms in smaller grains.

## UNDERSTANDING THE ROOT CAUSE

The hypothesis is that thermomechanical stresses

**Fig. 6** X-ray image of the SO8 defective device

**Fig. 7** Optical images of the pins and solder material

**Fig. 8** SEM images of the crack

generated by the different coefficients of thermal expansion (CTEs) are the cause of the failure. No clue was found to incriminate the fabrication process. The thermomechanical stresses that apply to the solder joint may stem from various causes:

- The CTE of the molding resin itself

- The different CTEs between the component and the PCB

- The position of the device on the PCB (far from the center)

Because a redesign of the PCB would have implied too many industrial consequences, the focus was on minor modifications, such as a change of resin or solder material.

## IMPACT OF RESIN CTE

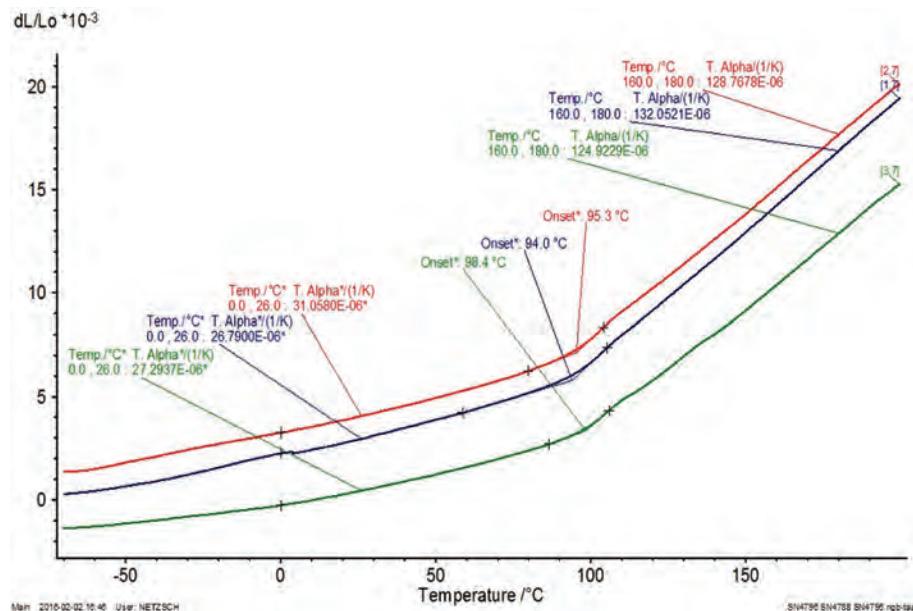

The resin CTE was measured with thermomechanical analysis (TMA) in the compression mode (Fig. 10). The postreticulation energy also was controlled with differential scanning calorimetry.

The results show that the resin is correctly reticulated, but the glass transition temperature ( $T_g$ ) is low compared to the application temperature range. Indeed, the  $T_g$  was measured at approximately 80 to 100 °C, but the DC/DC converter itself is supposed to self-heat at approximately 120 °C when operated.

If the operating temperature of the device exceeds the  $T_g$ , the CTE increases quickly. This phenomenon implies that the stress applied on the solder joints increases until recrystallization and a crack appear.

## IMPACT OF SOLDER JOINT THICKNESS

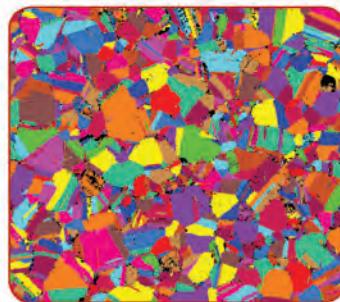

The plastic strain stored in the solder joints was controlled with the electron backscatter diffraction (EBSD) technique. This type of imaging is performed inside an SEM chamber. It is useful to acquire the orientation of the crystalline network for every pixel of an SEM image. Because strain induces local changes in the crystalline network

(continued on page 8)

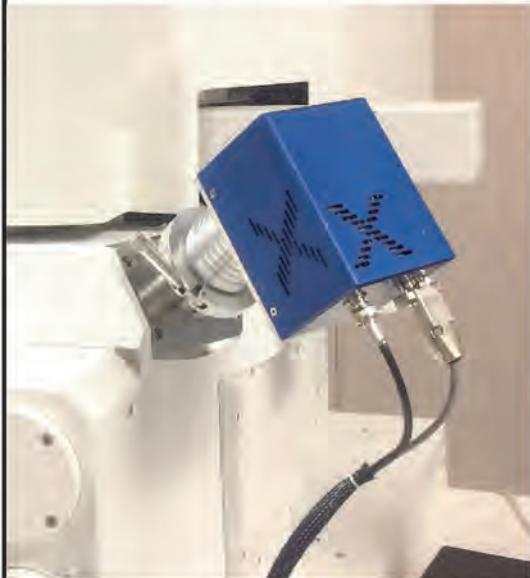

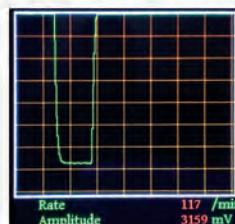

# Fast, accurate optical probing of frequency nodes

**EO Probing Unit** uses an incoherent light source to produce high-quality images without causing thermal damage to the sample chip. Probe waveforms with high S/N are generated in as little as 2 seconds.

**EOFM (electro-optical frequency mapping):**

This function captures images of nodes in isolated regions operating at a specific frequency. It makes it easier to observe whether or not the circuits are correctly switching.

**EOP (electro-optical probing):** This feature measures the timing of nodes through high-speed sampling. It improves the accuracy of failure point localization, thus enabling a smoother follow-up physical analysis.

## Applications

- Scan chain failure analysis

- Timing shift error observation

## Other features

- High-speed sampling up to 4 GHz

- Simultaneous two-channel image acquisition

- Easy-to-use software interface

- Retrofits with Hamamatsu Failure Analysis tools

Available for these systems:

PHEMOS | iPHEMOS | THEMOS |  $\mu$ AMOS | TriPHEMOS

Learn more at [www.hamamatsu.com](http://www.hamamatsu.com)

or call 858-210-6703

**HAMAMATSU**

PHOTON IS OUR BUSINESS

## FAILURE ANALYSIS OF DC/DC CONVERTERS: A CASE STUDY

(continued from page 6)

orientation, a map can be obtained. This technique is not quantitative, but a comparison can be made between two different devices. Here, the author tried to minimize the stress level on the solder material by increasing the thickness of the joint.

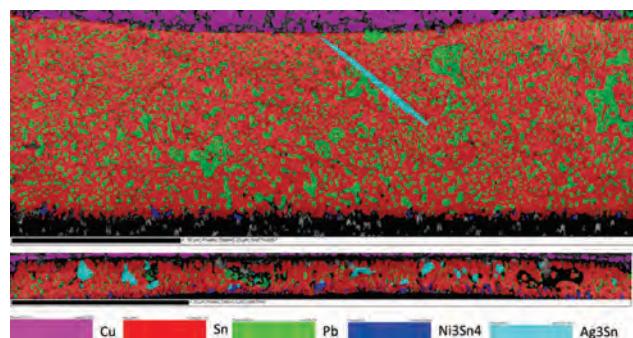

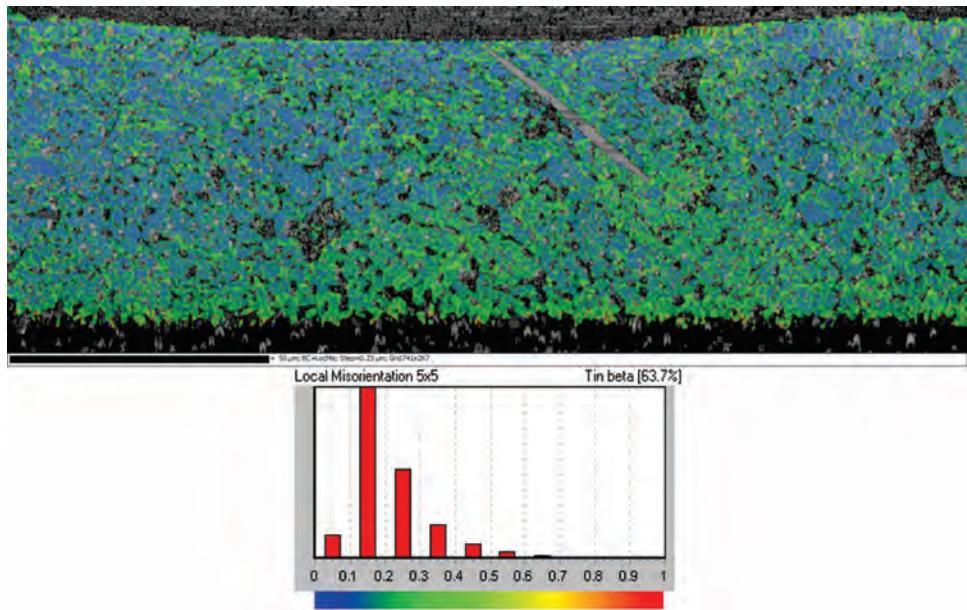

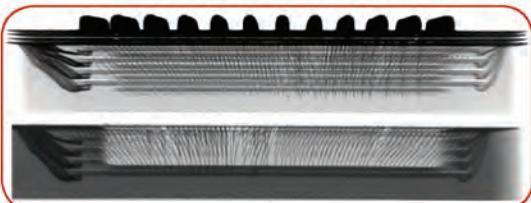

EBSD analysis also provides information about grain size, phase identification, and texture, which is the property of a material composed of grains oriented in the same crystalline direction. The following images present the results obtained on a thick solder joint along with a comparison to a thin solder joint. The material used is SnPbAg.

Figure 11 presents the phase mapping for thick and thin solder joints. No aging was applied on the devices prior to this analysis (no thermal cycles and only functional tests of the DC/DC converter). An important difference to note is the presence of needle-shaped silver precipitates ( $\text{Ag}_3\text{Sn}$ ) in the thick solder joint, whereas those precipitates are more circular in the thin joint. This

**Fig. 9** SEM images of the solder material between the pin and the pad. Recrystallization was found for both devices.

**Fig. 10** Strain-versus-temperature curves obtained by TMA

**Fig. 11** Phase identification for thick (above) and thin (below) solder joints

form factor modification is an indication of early stages of aging for the solder material.

Figures 12 and 13 show the local misorientation maps for both thick and thin joints. The colormap is representative of the crystalline misorientation from one pixel to the other, which can be interpreted as the strain stored in the material.

The histogram repartition shows that both the average and the maximum misorientation values are higher for the thin joint, which confirms that it was more affected by thermomechanical stresses. This quantitative observation is consistent with a more qualitative approach. The strain applied by the potting resin deformation is spread over a thinner joint, which implies more local stress.

## CONCLUSION

Failure analysis of a DC/DC converter was successfully undertaken. When defect localization is tricky—as for 3-D systems—a local probing approach is probably the best way to limit the region of investigation, until the defect is actually detected. This step is quite difficult to undertake. Overmolding resin etching must be nondestructive for both the component and the defect, so sample-preparation techniques must be adapted from device to device. In this case study, laser ablation provided good results,

**Fig. 12** Local misorientation mapping and associated histogram repartition for a thick solder joint

**Fig. 13** Local misorientation mapping and associated histogram repartition for a thin solder joint

assuming that the location to be opened is precisely known. Superimposition with an x-ray CT virtual slice of the PCB was useful for correctly placing the laser on top of the areas to be opened.

Understanding the root cause of the failure is another challenge. This article showed that thermomechanical

stresses applied to a solder joint generate the cracks. Those stresses originate from different phenomena: the resin CTE, the thickness of the solder joint, and its internal ability to withstand shear stress. All three parameters have been optimized to enhance the reliability of the DC/DC converter.

## ABOUT THE AUTHOR

**Jérémie Dhennin** received his Master's degree in micro- and nanophysics from the University of Paul Sabatier in Toulouse, France, in 2005. He joined NOVA MEMS as a research engineer working on multiphysical characterization and modeling of MEMS switches failure mechanisms. His research activities focused on radio-frequency MEMS switches reliability, failure analysis, and modeling, especially dealing with microcontact issues. Since 2012, Mr. Dhennin's technical scope has evolved to more generic reliability issues, dealing with other types of MEMS or electronic components. His managerial experience and broad technical scope allowed him to assume the Chief Executive Officer position at NOVA MEMS (now ELEMCA) in early 2013. He is still involved in many failure analysis processes, dealing with both electronic devices and MEMS components.

**BUEHLER**

## Reliable Solutions for **ELECTRONICS**

Electronics require targeted micro-sectioning and testing to identify substandard materials and verify that specifications are met during manufacturing. The electronics industry counts on Buehler equipment and consumables for PCB component verification, solder and joint analysis, sensor analysis, BGA sectioning and interconnect (IC) analysis.

### Industry Driven Solutions

Buehler develops products that save time and increases the quality of your samples.

#### IsoMet™ High Speed

The IsoMet High Speed Pro is an efficient precision saw with intuitive controls, a laser for accuracy and an automatic dressing system. The innovative machine and vise designs also make setup quick and simple.

#### EcoMet™/AutoMet™

EcoMet/AutoMet 300 is a robust grinder/polisher with durable construction and a 12" platen for faster grinding and reliability. When equipped with a PC Met accessory it is ideal for precise cross-sectioning of PWB through holes.

#### Consumables

Buehler has the right consumables to create accurate electronic samples. SamplKwick acrylic, CarbiMet PSA, TexMet, 3u Metadi Diamond Suspension, MicroCloth, MasterPrep are often the selected consumables for samples that meet the highest standards.

Strong Partner, Reliable Solutions

[edfas.org](http://edfas.org)

Buehler, An ITW Company

Worldwide Headquarters

41 Waukegan Road, Lake Bluff, IL 60044

Telephone: (847) 295-6500

[www.buehler.com](http://www.buehler.com) | [custserv@buehler.com](mailto:custserv@buehler.com)

# QuantumScope™

## Failure Analysis Microscopes

**FA engineers need proper tools in order to locate IC defects:**

- ohmic shorts

- impedance issues

- leakage currents

- leaky capacitors

- oxide defects

- damaged junctions

- resistive vias

- CMOS latch up

- ESD damage

- dynamic failures

***QFI suggests maximizing your defect capture rate...

NOT your capital expenditure rate.***

QuantumScope™ integrates XIVA™ LSIM, Thermal-HS hot spot detection, and emmi™ photoemission into a single, high-performance, microscope platform. Semiconductor FA is more efficient and more accurate when the DUT remains mounted in a single diagnostic tool during all three of these FA microscope techniques. QuantumScope™ eliminates the need for multiple separate systems, freeing capital for other requirements. QFI systems are modular in design and generally compatible with field upgrade.

Quantum Focus Instruments Corporation

2385 La Mirada Drive • Vista CA 92081

Phone: +1 (760) 599-1122

Fax: +1 (760) 599-1242

e-mail: [sales@quantumfocus.com](mailto:sales@quantumfocus.com)

<http://www.quantumfocus.com>

# NANOSCALE CAPACITANCE AND CAPACITANCE-VOLTAGE CURVES FOR ADVANCED CHARACTERIZATION OF ELECTRICAL PROPERTIES OF SILICON AND GaN STRUCTURES USING SCANNING MICROWAVE IMPEDANCE MICROSCOPY (sMIM)

Oskar Amster, Stuart Friedman, Yongliang Yang, and Fred Stanke

PrimeNano, Inc.

amster@primenanoinc.com

## OVERVIEW

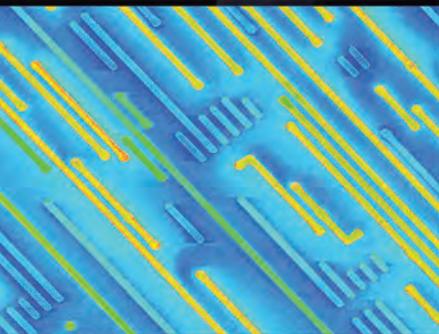

A relatively new electrical mode, scanning microwave impedance microscopy (sMIM), measures a material's change in permittivity and conductivity at the scale of tens of nanometers.<sup>[1]</sup> The use of atomic force microscopy (AFM) electrical measurement modes is a critical tool for the study of semiconductor devices and process development. More specifically, the application of AFM electrical modes is an important tool for characterizing semiconductor devices during process development and failure analysis. The AFM-based electrical measurement techniques, such as scanning capacitance microscopy (SCM) and scanning spreading-resistance microscopy,<sup>[2,3]</sup> have shown value for dopant profiling in semiconductor samples with sub-50 nm spatial resolution. However, there has been no single scanning probe technique capable of quantifying at submicron dimensions the local electrical properties of materials (dielectric constant and conductivity) with the sensitivity and dynamic range required by the semiconductor industry and research communities.

Scanning microwave impedance microscopy provides the capability to directly probe a sample's permittivity and conductivity at submicron geometries. Scanning microwave impedance microscopy provides the real and imaginary impedance ( $Re(Z)$  and  $Im(Z)$ , respectively) of the probe-sample interface impedance. By measuring the reflected microwave signal of a sample of interest imaged with an AFM, one can capture in parallel the variations in permittivity and conductivity and, for doped

“SCANNING MICROWAVE IMPEDANCE MICROSCOPY PROVIDES THE CAPABILITY TO DIRECTLY PROBE A SAMPLE'S PERMITTIVITY AND CONDUCTIVITY AT SUBMICRON GEOMETRIES.”

semiconductors, the variations in depletion-layer geometry.<sup>[4,5]</sup> Scanning capacitance microscopy, an existing technique for characterizing doped semiconductors, modulates the tip-sample bias and detects the tip-sample rate of change of capacitance with bias voltage using a lock-in amplifier. A previous study compared sMIM to SCM and highlighted the additional capabilities of sMIM,<sup>[6,7]</sup> including examples of nanoscale capacitance-voltage curves.

The initial implementation of sMIM focused on the relative measurement of local permittivity and conductivity at a sample surface. The capability to directly image the local variation of a sample's electrical properties at spatial resolutions of tens of nanometers has stimulated new areas of research. For technologically and scientifically important materials, such as graphene,<sup>[8]</sup> carbon nanotubes,<sup>[9]</sup> ferroelectric domains,<sup>[10,11]</sup> and doped semiconductors,<sup>[12-14]</sup> researchers are actively using this technique to gain new understanding of materials systems behavior.

**Fig. 1** Schematic of the PrimeNano ScanWave electronics with a matching circuit and shielded coaxial line to the probe-sample interface

The natural progression and general interest in the user community is to extend the sMIM capabilities to quantitative measurements. This article presents recent analytical and finite-element modeling developments of tip-bias-dependent depletion-layer geometry and impedance. These are compared to experimental results on reference samples for both silicon- and GaN-doped staircases to systematically validate the response of the sMIM-C channel to the doping concentration.

## INTRODUCTION

In a standard sMIM experiment, microwaves are coupled through a custom AFM cantilever to the probe tip, where they interact as evanescent waves with the portion of the sample immediately under the tip. A fraction of the microwaves is reflected, and the amplitude and phase (or equivalently, the real and imaginary parts) of the reflection are determined by the local electrical properties of the sample. For a linear sample (e.g., a dielectric or metallic material), the permittivity and conductivity determine the reflection, while for a nonlinear sample (e.g., a doped semiconductor), the tip-bias-dependent depletion-layer structure contributes significantly. As a result, sMIM measurements can provide valuable nanoscale information about semiconductor devices, processes, and defects.

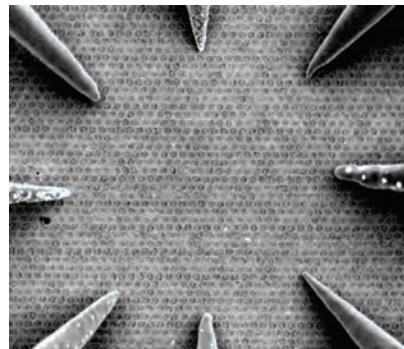

A custom AFM probe is mounted in a specialized holder so that there is a coaxial connection from the microwave source to the AFM probe tip. The specialized probe module with matching circuit is then fitted to a standard AFM. The AFM typically operates in contact mode for imaging but can also be used in intermittent and tapping modes. The sMIM probes contain a multilayer cantilever with a shielded signal line connecting a contact pad on the carrier chip to the metallic tip at the end of the cantilever. The holder connects to the contact pad and couples 3 GHz microwaves from the sMIM measurement electronics to the AFM probe carrier chip, where they propagate along the signal line in the cantilever to the conductive tip.<sup>[15]</sup> The reflected signal retraces the same path. This configuration is illustrated schematically in Fig. 1. The

probes, probe interface module, and electronics are part of a commercial ScanWave sMIM module (PrimeNano, Inc.). The sMIM is adapted to the most common commercial AFM platforms.<sup>[4,5]</sup>

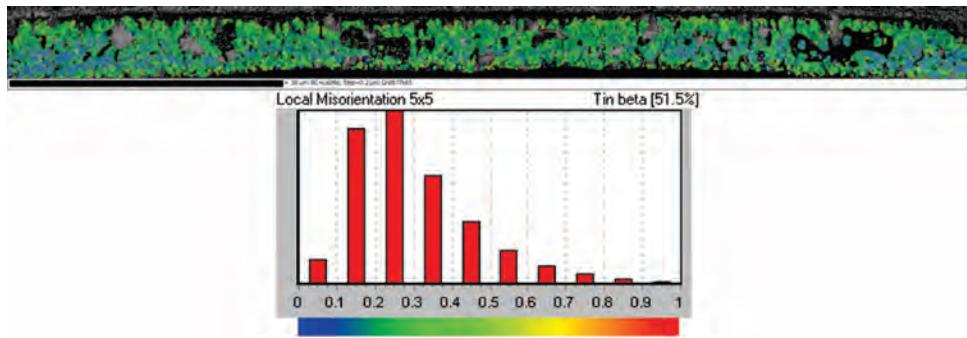

The sMIM-C measured on various bulk dielectrics shows a clear linear relationship between sMIM-C and the log of the permittivity.<sup>[4,5,16]</sup> The red squares shown in Fig. 2 are from a model that originates with a finite-element calculation of the tip-sample admittance for the conical geometry of the sMIM probe. The origins of the  $\log(\epsilon)$  dependence can be seen in analytical models for spherically terminated conical tips above and in contact with linear materials, documenting the origin of the log dependence published by other researchers.<sup>[17]</sup>

For sMIM measurements on nonlinear materials, such as a doped semiconductor, the tip-sample bias influences the tip-sample impedance, or, more conveniently, the reciprocal of the tip-sample impedance, the tip-sample admittance,  $Y_{TS}$ . As with linear samples, the sMIM signals are still proportional to the imaginary and real parts of  $Y_{TS}$ , the capacitance and conductance below the tip-sample interface, but the capacitance and conductance now depend not only on the local permittivity and conductivity of the sample under the tip but also on the geometry of

**Fig. 2** Graph of the numerically modeled admittance versus the dielectric value (in red) with the experimentally measured sMIM versus the dielectric value (in blue) from a group of bulk crystal dielectric samples

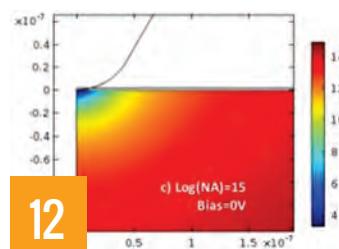

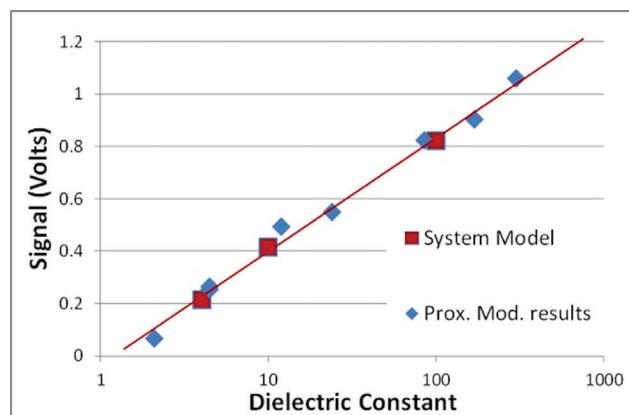

the depletion layer. The depletion-layer geometry, in turn, depends on the tip-sample direct current or low-frequency voltage and on the doping level of the semiconductor. Analytical solutions exist for one-dimensional geometries, and these can be used to model the results from macroscopic parallel-plate metal oxide semiconductor (MOS) structures. Figure 3 shows the classic parallel-plate model for describing a MOS device. A lumped-element

approximation for an sMIM tip on an oxide-coated semiconductor and expressions from the delta depletion model for depletion-layer thickness<sup>[17]</sup> are shown in Fig. 3.

Because depletion-layer geometry has a strong impact on sMIM signals and because the depletion-layer geometry varies with tip-sample voltage and with doping, varying the tip-sample voltage is a way to characterize semiconductor materials and devices, particularly the local

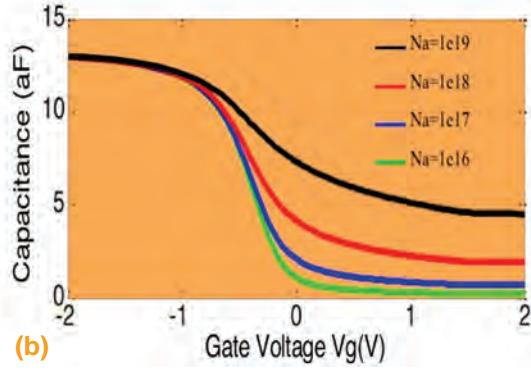

**Fig. 3** (a) Schematic of the classical MOS device configuration with the sMIM probe contacting a sample surface modeled as two series capacitors. The equations describe the relationship of the capacitance (and therefore the sMIM) measurement on the depletion-layer thickness and doping concentration. (b) Numerically generated capacitance-voltage curves from the parallel-plate model illustrate sMIM's sensitivity to semiconductor doping level.

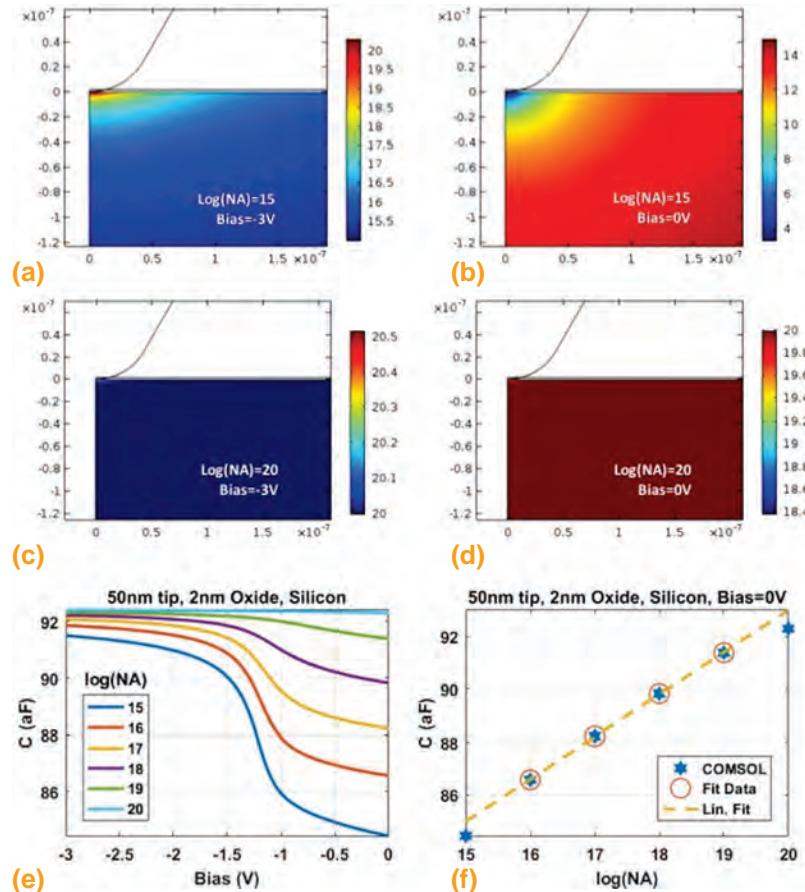

**Fig. 4** (a-d) Finite-element model (FEM) predictions of the majority carrier hole density in the presence of marked biases on an sMIM probe for the marked p-type doping densities in silicon. Many more such simulations led to (e) FEM predictions of C-V curves, with the dopings specified by the legend. (f) Calibration of the probe tip's capacitance over the various doped samples as a function of their doping density

doping level under the tip (or electrode, in the case of patterned samples with electrodes present). This is similar to capacitance-versus-voltage curves from macroscopic samples commonly used to characterize semiconductor materials and test structures. Figure 3(b) presents the classical solution to the parallel-plate model, numerically generated here for a range of doping concentration levels. This model is incomplete for describing the geometries for AFM probe-sample interactions.

Similar to what was observed in the measurements of linear dielectrics shown in Fig. 2, where the sMIM signal is proportional to  $\log(\epsilon)$ , experimental data from doped semiconductors show sMIM signals varying linearly with  $\log([\text{doping concentration}])$ . To confirm the origins of the  $\log([\text{doping concentration}])$  behavior, finite-element modeling was used to assess the depletion-layer geometry for a conical tip and how this geometry varies for both doping and applied gate (i.e., tip) voltage. Figure 4(a) shows the results for one doping level.

The finite-element models also allow calculation of the tip-sample capacitance for each doping level and gate voltage, resulting in capacitance-voltage (C-V) curves for the geometry of an sMIM probe on an oxide-coated semiconductor (Fig. 4e). Experimental data presented subsequently in this article resemble the model results, indicating that most critical physics are accounted for by the models. Figure 4(f) shows that the capacitance seen and measured by sMIM is linear in log doping over several orders of magnitude for dopings of practical importance, enabling the possibility of calibrating sMIM results to invert for doping density.

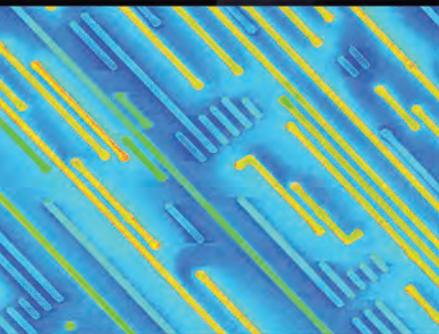

## EXAMPLES OF sMIM AND C-V ON SILICON SAMPLES

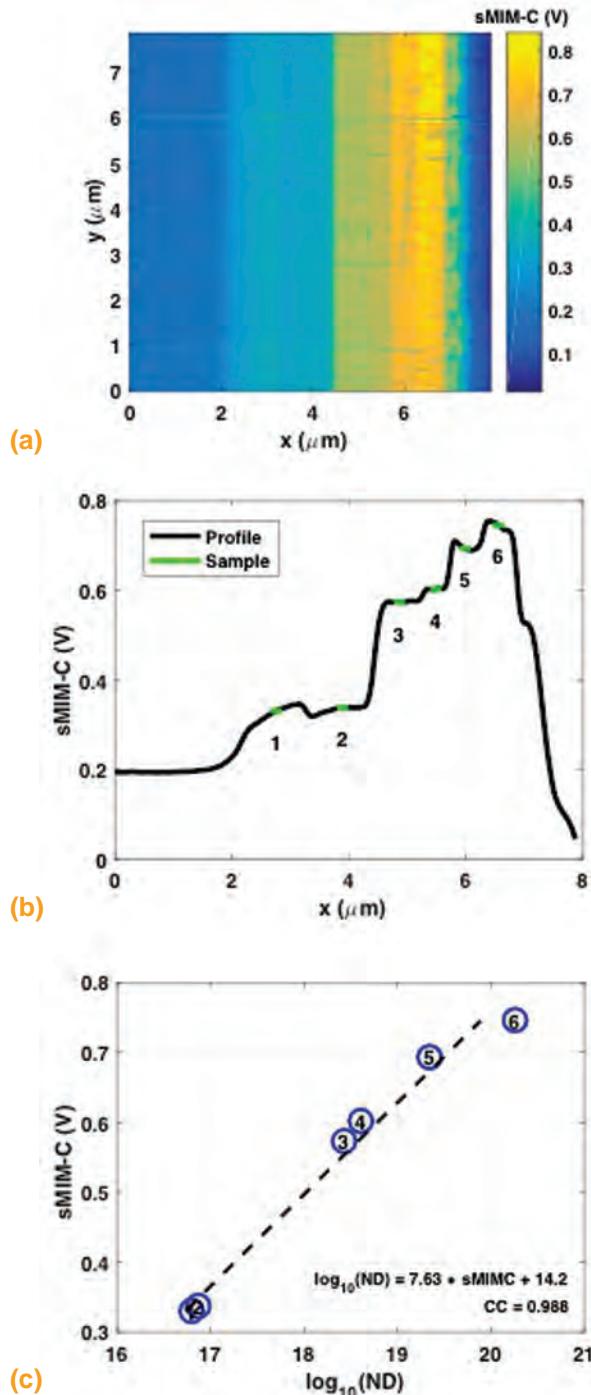

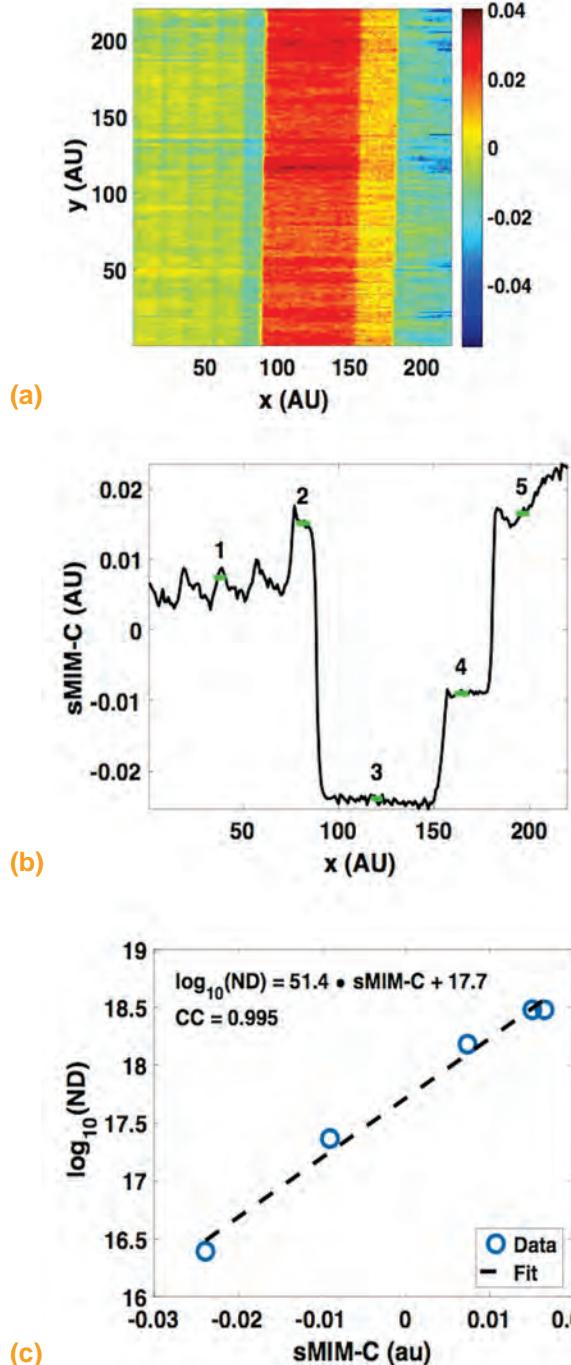

It has been shown in previous work<sup>[4,5]</sup> that sMIM-C is linear with the  $\log N_A$ . Results presented in this section show application of sMIM-C's linear relationship to  $\log N_A$  for quantification of sMIM-C doping concentration in log units. An IMEC *n*-type doped staircase was used as a calibration sample. The IMEC staircase is measured using ScanWave sMIM to determine a calibration curve that can then be applied to an unknown sample to convert sMIM-C to units of doping concentration. Figure 5(a) shows the sMIM-C image of the IMEC staircase doping standard. The sample was measured using a two-pass method with no applied bias. The data are collected line by line; the first line is in contact mode, and the second pass is at a height 100 nm above the sample surface. The difference image is shown in Fig. 5(a). An average profile is shown in Fig. 5(b). The resulting profile shows excellent correlation to the

IMEC published doping concentration data. The average profile graph (Fig. 5b) highlights where the average sMIM-C value was calculated for the graph in Fig. 5(c), plotting the measured sMIM-C versus known doping concentration.

Due to the very linear response of the sMIM-C versus log doping concentration, one can use the corresponding

**Fig. 5** (a) Processed sMIM-C image of an *n*-type IMEC staircase. (b) Average profile with “calibration samples” highlighted in green. (c) Plot of sMIM-C calibration values versus published values of log doping. The linear fit is a calibration that can be applied to subsequent unknown doped samples.

curve (Fig. 5c) as the calibration to convert sMIM-C measured on a device sample to log doping.<sup>[10]</sup>

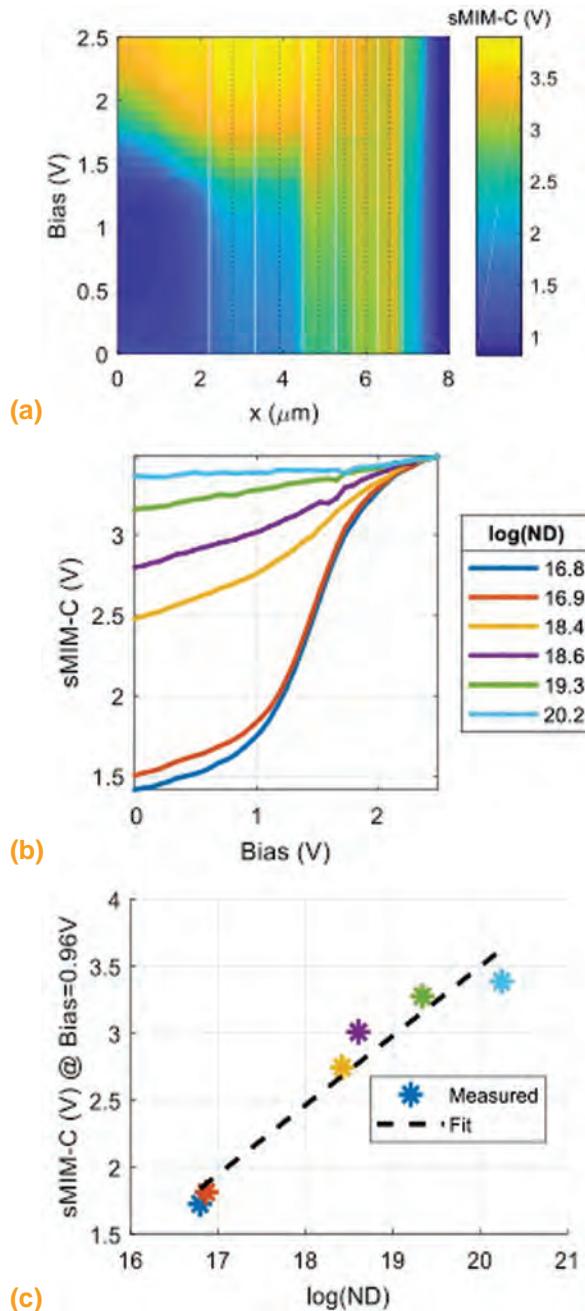

Figure 6(a) presents the results of nano-C-V curves from the IMEC staircase, verifying that the nanoscale response matches the theory discussed in the introduction of this article. This “image” is from multiple sMIM scans over the same 8- $\mu\text{m}$ -length line on the sample, collected as the bias voltage scans from 0 to 2.5 V. The demarcations of the doped regions are marked with vertical white lines, separated by exactly the widths of the regions published by IMEC for this sample. The data for the six C-V curves in Fig. 6(b) were taken from the vertical dashed black lines, which are placed exactly midway between the white lines. The C-V curves were shifted so they all have the same sMIM value at the most positive voltage, quite deep into accumulation. These empirical C-V curves for *n*-type silicon closely resemble the mirror images of the theoretical C-V curves for a *p*-type silicon, as they should. (The sMIM-C is proportional to the admittance at the tip/sample interface and therefore to the capacitance.) Figure 6(c) shows the sMIM-C values from the C-V curves in Fig. 6(b) at the tip-sample voltage with the highest doping sensitivity (0.96 V), and they vary linearly with log doping density over approximately 4 orders of magnitude. The derived linear calibration has the formula  $\log(\text{ND}) = 1.83 \times \text{sMIM-C} + 19.9$ , with a correlation coefficient of 0.972.

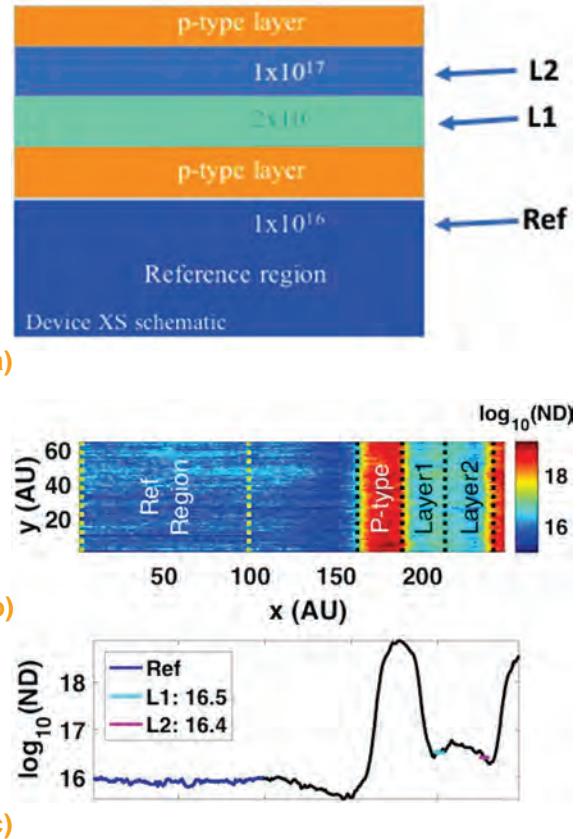

## sMIM REFERENCE APPLIED TO A GaN DEVICE

This section extends the methods discussed previously on doped silicon systems to III-V semiconductor materials. An *n*-type GaN staircase reference sample was prepared using an *n*-type GaN substrate and growing four epitaxial layers with varying doping levels. Two of the steps, 2 and 5, have the same doping concentration, as shown in Fig. 7(b). The sample was independently measured using secondary ion mass spectrometry (SIMS) to verify the doped step values, and these values were used for calibration. Figure 7(a) shows the sMIM-C image, with roughly vertical regions representing the individual steps. Using the technique described previously, an average profile of the steps is used to extract the sMIM step value (Fig. 7b), which is then plotted versus log doping to establish the calibration curve (Fig. 7c).

After calculating the calibration curve on the calibration sample, it can now be applied on an “unknown” GaN device to convert the sMIM to units of log doping concentration. The test device is a multilayer structure with both *n*- and *p*-type doped regions. This article concentrates

on the *n*-type regions, because the calibration staircase is *n*-type only.

Figure 8(a) shows a cross-sectional schematic of the “unknown” device. The schematic identifies three regions of interest on the sample that are *n*-type doped regions:

**Fig. 6** (a) Image of an 8  $\mu\text{m}$  line scanned repeatedly while the bias voltage swept from 0 to 2.5 V. The vertical white lines demarcate the doped regions in this cross-sectional sample. The vertical dotted black lines indicate where values were extracted to give C-V curves. (b) C-V curves extracted from (a). The curves have been shifted vertically so they meet at bias = 2.5 V, deep into accumulation. (c) Calibration from sMIM-C to  $\log(\text{ND})$  at bias = 0.96 V, where sMIM-C has the most doping contrast

the reference region, L1, and L2. Figure 8(b) shows an sMIM-C image of the “unknown” device. The same three regions of interest are marked with dotted lines and labeled. The image is converted to units of log doping concentration after applying the calibration curve from Fig. 7(c).

**Fig. 7** Measurement of a GaN epilayer *n*-type doped staircase. (a) sMIM-C image. (b) Average profile of the aligned image, with the highlights showing calibration values. (c) sMIM-C versus doping concentration in log units. The graph shows good linearity over the range of doping and demonstrates the linear relationship of sMIM-C versus log(ND) for a nonsilicon semiconductor material.

Figure 8(c) is the average profile extracted from the sMIM-C image in Fig. 8(b). The “reference region” of the “unknown” device has the same doping concentration as step 3 of the calibration sample. The common value allows compensation for the potential offsets that may occur due to system drift or systematic errors during the measurements. The calibration curve doping concentration value is shifted to pass through the reference value on the device sample and then applied to the whole profile to calculate doping concentrations.

The comparison of the nominal values with the calibrated sMIM values shows that the ratio of L1 to L2 is 2.0 for the SIMS and 1.3 for the sMIM, respectively. The result shows that sMIM is sensitive to the doping concentration difference in the two regions, differing by 0.1 log units. The measured values are lower than the SIMS reference values. The authors speculate that the variation can be caused by

**Fig. 8** (a) Cross-sectional schematic of a GaN device. The sample is labeled with nominal doping values independently obtained by SIMS measurement to verify the nominal doping levels before cross sectioning and measuring with sMIM. (b) sMIM image of the “unknown” sample with color scale converted to *n*-type doping concentration using the calibration data from Fig. 7. (c) Average profile of the sMIM data, where the Ref line is highlighted. The  $1 \times 10^{16}$  region has the same doping concentration as step 3 of the reference sample.

the difference in measured doping concentration, because SIMS measures the implanted doping density, and sMIM-C measures the activated doping concentration, as well as possible systematic variation during the measurements that could account for the discrepancy. It is expected for GaN that the activated doping concentration would be lower than the implanted density.

The application of sMIM to a cleaved cross-sectional GaN device sample demonstrates the robustness of the method and the flexibility to measure doping levels on an unknown device sample using a known staircase for calibration of III-V materials. Further refinements are ongoing.

## SUMMARY

Scanning microwave impedance microscopy as a new mode for electrical measurements integrated to an AFM can address the needs of the semiconductor and failure analysis communities by providing increased sensitivity to investigate semiconductor devices for current and next-generation technologies. Adoption of sMIM will enhance the available toolkit, especially in addressing quantification of doped semiconductors and dielectric materials.

This article presents examples of some of the benefits of the sMIM technology: linear correlation to the log of dielectric coefficient; linear response to the log of doping concentration; visualization of metal, doped materials, and dielectrics in the same image; nanoscale C-V curves; and quantification of doping concentration on different classes of semiconductor materials.

The AFM probes present specific challenges during measurements. This article shows results validating the authors' models with comparison of the classic one-dimensional MOS model with a three-dimensional finite-element analysis cone-shaped model, confirming that using an AFM probe as an electrode for nanoscale C-V curves is different from those acquired with parallel-plate geometry but has similar potential for yielding quantitative characterizations. This article also shows that C-V curves can be measured from doped semiconductors and that they are consistent with what is predicted by theory for this type of three-dimensional geometry.

The article also shows that single-bias images and single-point C-V measurements on an IMEC *n*- and *p*-type doped staircase sample are consistent and therefore can be used together to give an enhanced, quantitative view of a sample's doping state. In addition, it has been shown that sMIM measurements on III-V semiconductor materials and silicon behave very similarly, so methods developed for the latter can be applied to the former; namely, a calibration from a known staircase sample can

be applied to the sMIM image of an "unknown" device sample to estimate doping concentrations.

## REFERENCES

1. Y. Yang, E.Y. Ma, Y.-T. Cui, A. Haemmerli, K. Lai, W. Kundhikanjana, N. Harjee, B.L. Pruitt, M. Kelly, and Z.-X. Shen: "Shielded Piezoresistive Cantilever Probes for Nanoscale Topography and Electrical Imaging," *J. Micromech. Microeng.*, 2014.

2. N. Duhayon, T. Clarysse, P. Eyben, W. Vandervorst, and L. Hellemans: "Detailed Study of Scanning Capacitance Microscopy on Cross-Sectional and Beveled Junctions," *J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct.*, 2002, 20(2).

3. N. Duhayon, P. Eyben, M. Fouchier, T. Clarysse, W. Vandervorst, D. Álvarez, S. Schoemann, et al.: "Assessing the Performance of Two-Dimensional Dopant Profiling Techniques," *J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct.*, 2004, 22(1).

4. S. Friedman, O. Amster, and Y. Yang, "Recent Advances in Scanning Microwave Impedance Microscopy (sMIM) for Nano-Scale Measurements and Industrial Applications," *Proc. SPIE*, 2014, 9173, id. 917308.

5. J.R. Matey and J. Blanc: "Scanning Capacitance Microscopy," *J. Appl. Phys.*, 1985, 57(5), pp. 1437-44.

6. B. Drevniok, St.J. Dixon-Warren, O. Amster, S.L. Friedman, and Y. Yang: "Extending Electrical Scanning Probe Microscopy Measurements of Semiconductor Devices Using Microwave Impedance Microscopy," *Proc. 41st Int. Symp. Test. Fail. Anal. (ISTFA)*, 2015, p. 77.

7. Z.Y. Wang et al.: "Evanescence Microwave Probe Measurement of Low-k Dielectric Films," *J. Appl. Phys.*, 2002, 92, p. 808.

8. E.Y. Ma, M.R. Calvo, J. Wang, B. Lian, M. Mühlbauer, C. Brüne, Y.-T. Cui, et al.: "Unexpected Edge Conduction in Mercury Telluride Quantum Wells under Broken Time-Reversal Symmetry," *Nature Commun.*, 2015.

9. E. Seabron, S. McLaren, X. Xie, S.V. Rotkin, J.A. Rogers, and W.L. Wilson: "Scanning Probe Microwave Reflectivity of Aligned Single-Walled Carbon Nanotubes: Imaging of Electronic Structure and Quantum Behavior at the Nanoscale," *ACS Nano*, 2015.

10. E.Y. Ma, Y.-T. Cui, K. Ueda, S. Tang, K. Chen, N. Tamura, P.M. Wu, J. Fujioka, Y. Tokura, and Z.-X. Shen: "Mobile Metallic Domain Walls in an All-In-All-Out Magnetic Insulator," *Science*, 2015, 350(6260), p. 538.

11. A. Tselev, P. Yu, Y. Cao, L.R. Dedon, L.W. Martin, S.V. Kalinin, and P. Maksymovych: "Microwave A.C. Conductivity of Domain Walls in Ferroelectric Thin Film," *Nature Commun.*, May 2016, pp. 1-9, doi:10.1038/ncomms11630.

12. H.P. Huber, I. Humer, M. Hochleitner, M. Fenner, M. Moertelmaier, C. Rankl, A. Imtiaz, et al.: "Calibrated Nanoscale Dopant Profiling Using a Scanning Microwave Microscope," *J. Appl. Phys.*, 2012, 111(1).

13. St.J. Dixon-Warren and B. Drevniok: "Practical Quantitative Scanning Microwave Impedance Microscopy," *Proc. 42nd Int. Symp. Test. Fail. Anal. (ISTFA)*, 2016.

14. W.S. Hu, J.H. Lee, M.H. Kao, H.W. Yang, P. Dewolf, and O. Amster: "Device Dielectric Quality Analysis and Fault Isolation at the Contact Level by Scanning Microwave Impedance Microscopy," *Proc. 42nd Int. Symp. Test. Fail. Anal. (ISTFA)*, 2016.

15. Y.L. Yang, K.J. Lai, Q.C. Tang, W. Kundhikanjana, M. Kelly, Z.X. Shen, and X. Li: "A Shielded Cantilever-Tip Microwave Probe for Micro/Nano Surface Imaging of Conductive Properties," *2011 IEEE 24th Int. Conf. Micro Electro Mech. Syst. (MEMS)*, 2011.

16. K. Lai, W. Kundhikanjana, M.A. Kelly, and Z.X. Shen: "Calibration of Shielded Microwave Probes Using Bulk Dielectrics," *Appl. Phys. Lett.*, 2008.

17. R. Pierret, *Semiconductor Device Fundamentals*, 2nd ed., Pearson, 1995.

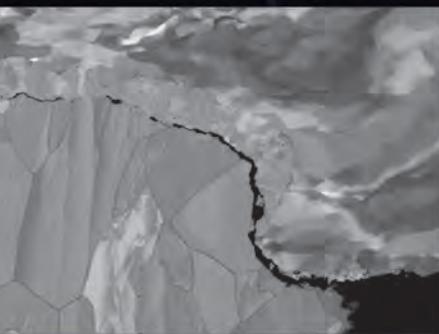

(continued on page 20)

# Cross-sectioning without destroying your sample.

ZEISS Xradia 520 Versa

Image courtesy of AMD Failure Analysis Lab, Singapore

Visit us at

ISTFA

booth #725

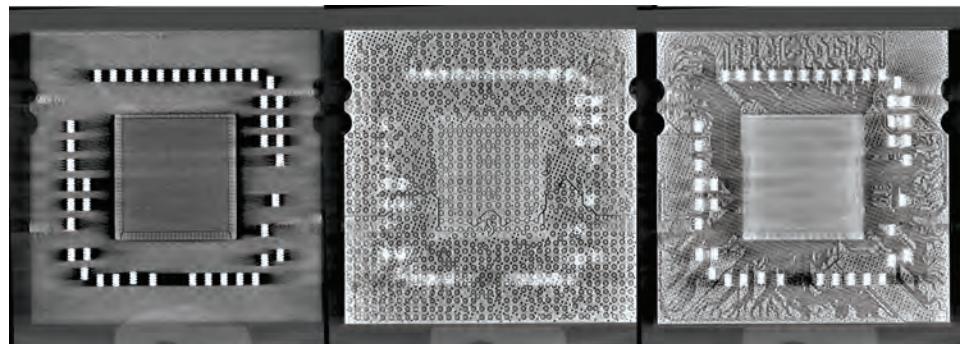

Virtual cross section

## Identify and visualize failure locations in advanced packaging technologies.

Imagine seeing buried faults in high resolution ... non-destructively. ZEISS X-ray microscopes (XRM) provide 3D tomographic data with submicron resolution and contrast for a wide variety of electronics samples, regardless of sample size. With ZEISS XRM, resolution does not degrade as sample sizes increase so whether you are visualizing a 10 mm flip chip package or a 300 mm wafer, you can maintain close to one-micron resolution for any point on your sample.

[www.zeiss.com/semiconductor-process-control](http://www.zeiss.com/semiconductor-process-control)

Virtual planar section

## NANOSCALE CAPACITANCE AND CAPACITANCE-VOLTAGE CURVES (continued from page 18)

### ABOUT THE AUTHORS

**Oskar Amster** has 20 years of experience working with analytical instruments and metrology tools. His background is in applications development, strategic marketing, and product development. He has extensive experience working in atomic force microscopy, stylus profilers, and optical profiler instruments. Prior to joining PrimeNano, Inc., Oskar was Product Marketing Manager at KLA-Tencor and held positions at Ambios Technology, Ametek Taylor Hobson, Multiprobe, Micron Force Instruments, and Topometrix. He has an M.S. in materials engineering and a B.S. in physics from California Polytechnic State University, San Luis Obispo.

**Stuart Friedman** has engaged in academic and industrial research in a variety of areas, including image processing, surface science, electron optics, bio-medical instrumentation, and bio-physical simulation. He currently serves as Chief Technology Officer of PrimeNano, Inc., a Silicon Valley instrumentation startup focused on commercial implementation of scanning microwave impedance microscopy for research and commercial applications. Before co-founding PrimeNano, Dr. Friedman founded and led a research and development and systems engineering consulting firm in Silicon Valley, helping transition complex systems to commercial reality for startups as well as Fortune 500 clients. Prior to that, he held research and development, systems architecture, and technical leadership roles at Gatan, Inc., Etec Systems, KLA-Tencor, MDS Sciex, and Signature Bioscience. Dr. Friedman holds a Ph.D. in applied physics from Stanford University, an M.Phil. in physics from Cambridge University, and a B.S.E. in engineering physics from Cornell University.

**Yongliang Yang** has been conducting research on scanning probe microscopy technology for the past five years. He has also spent more than 10 years doing research on MEMS devices. Before joining PrimeNano, Inc. in 2014 as a research and development scientist, Dr. Yang was a postdoctoral student at Stanford University, developing scanning microwave impedance microscopy (sMIM) technology and studying electrical properties of materials with sMIM. Dr. Yang has a B.S. degree from Peking University and a Ph.D. from the Chinese Academy of Sciences. He holds four patents and is the author of more than 40 publications.

**Fred Stanke** has done research and development of metrology and inspection systems for a wide range of applications. For his Ph.D. dissertation at Stanford University, he developed ultrasonic metrology to nondestructively measure the grain sizes of metals. He did research with Schlumberger Limited on using ultrasound to inspect oil well casings for their capability to provide hydraulic isolation. At the startup Sensys Instruments, Dr. Stanke headed the technical team to develop an optical system using scatterometry to measure the critical dimensions of integrated circuits. He accompanied that product when Tokyo Electron Limited bought it to integrate into semiconductor clean tracks to improve and shorten the control loop for microlithography. At PrimeNano Inc., Dr. Stanke does research and development to allow scanning microwave impedance measurements to quantify properties such as the doping concentrations of semiconductors.

Advertise in *Electronic Device Failure Analysis* magazine!

For information about advertising in *Electronic Device Failure Analysis*, contact

Erik Klingerman, National Account Manager; tel: 440.840.9826;

e-mail: [Erik.Klingerman@asminternational.org](mailto:Erik.Klingerman@asminternational.org).

Current rate card may be viewed online at [asminternational.org/mediakit](http://asminternational.org/mediakit).

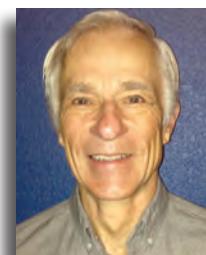

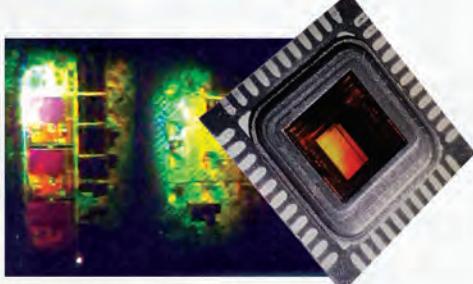

# SEMICAPS ARSIL

for

Photon Emission Microscopy (PEM)

\*Backside Emission of Macro Lens

Backside Emission on

**SEMICAPS ARSIL**

\*Microelectronics Reliability Vol 73, June 2017. Pages 76-91

[www.semicaps.com](http://www.semicaps.com)

Your Solutions Partner

**SEMICAPS**

Excellence in Innovation

# PRODUCT CIRCUIT VALIDATION AND FAILURE DEBUG: A SEMICONDUCTOR FOUNDRY CAN HELP

Edy Susanto, S.H. Goh, Edmund C. Manlangit, and Jeffrey Lam

GLOBALFOUNDRIES, Technology Development, Product, Test, and Failure Analysis,

Singapore

[szuhuat.goh@globalfoundries.com](mailto:szuhuat.goh@globalfoundries.com)

## INTRODUCTION

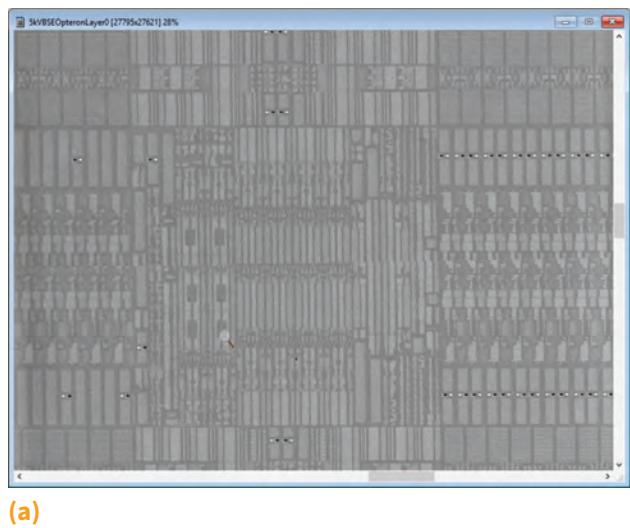

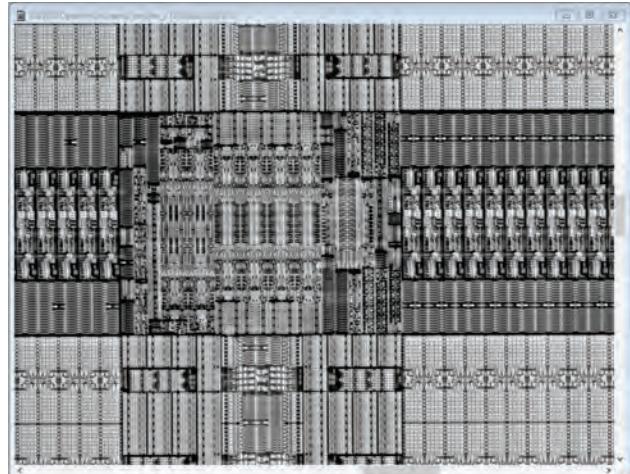

Before a product enters mass production, a series of design validation and debugging procedures precede as part of the qualification process. Generally, they are broadly classified into simulation-based presilicon validation and postsilicon validation using prototype samples tested under the actual system environment. Despite the painstaking efforts that employ varied simulators and emulators to ensure a clean design tapeout prior to manufacturing, bugs that escape presilicon verification are on the rise<sup>[1-3]</sup> due to increasing design complexity in modern chips and a widening discrepancy between simulation and actual functional performance as process technologies advance.<sup>[4,5]</sup> In general, there are two types of design bugs. Logic or functional bugs are caused by design errors or insufficient validation coverage. Electrical or circuit bugs that manifest under certain operating conditions can be caused by design marginalities and process variations. As a statistical reference, it was reported that approximately 2 and 10% of logic and circuit bugs, respectively, were discovered and fixed at postsilicon validation.<sup>[1]</sup> This situation is expected to be worsened by recent rising trends of third-party intellectual property (IP) modules integration, increasing clock speeds, narrowing design windows due to tightened design rules, and more aggressive production schedules. In addition, there have also been ongoing discussions to enter tapeout early and interrogate the bugs on actual silicon; the justification is a potential shortening of the entire design verification process.<sup>[6,7]</sup> This explains why postsilicon validation is gaining more traction and why increased efforts are critical to ensure no escapes into production after this final stage of verification.<sup>[8-10]</sup>

Postsilicon validation encompasses evaluating the

functional response of the prototype units per se and their interactions at a system-level platform. Unlike presilicon validation, the tests are usually performed at speed, offering faster lead time. However, this advantage comes at a trade-off of limited observability and intensified debug complexity, because internal nodes cannot be easily assessed and modified on silicon. To achieve debugging, design for testability (DFT) elements such as the IEEE Standard 1149.1 test access port (JTAG),<sup>[11]</sup> IEEE Standard 1687 (I-JTAG),<sup>[12]</sup> and scan-based architecture are leveraged to capture and shift data out of circuit internal nodes.<sup>[13]</sup> For elusive bugs that only manifest under certain operational time lapse or conditions, a more effective technique is employed that traces internal circuit signals continuously during testing.<sup>[14]</sup> Although these techniques are well established and efficient, failures in the field, especially related to design marginalities, are inevitable due to shortcomings in test coverage or advanced fault models. Debugging these test escape fails that occur sporadically is challenging but also part of the postsilicon validation process. Over the last decade, the tester-based laser scanning optical microscope tool has been increasingly adopted as an added approach. It is mainly used to debug internal circuit logic and speed paths at large. Some techniques related to such applications are waveform probing of internal nodes<sup>[15-18]</sup> and logic state mapping.<sup>[19]</sup>

Fundamentally, be it software- or hardware-based approaches to postsilicon failure debug, an in-depth knowledge of the DFT or design for debug circuitries in the integrated circuit (IC) is requisite. Therefore, it is natural that such activities can only be conducted by design centers and not IC contract manufacturers (foundry). Product time-to-mass-production thus relies solely on the available resources within the design centers to fix the errors.

## ROLE OF SEMICONDUCTOR FOUNDRY IN FIRST-SILICON VALIDATION AND FAILURE DEBUG

A semiconductor foundry is strongly motivated by revenue generation to ensure that a design tapeout releases to production from technology development in the shortest possible time. However, besides the advances in design-for-manufacturing efforts to increase the odds of first-silicon success, postsilicon validation and design debug, as a last gate, is usually noncollaborative in nature between design centers and foundries. By tradition, the latter are expected to focus only on process fixes for the reason mentioned in the previous section, while the former assume the responsibilities for design-related matters. Moving forward, the clear demarcation between process or design bugs is becoming more obscured due to the tightening margins in both aspects, and it is time for a paradigm shift for both facilities to step out of their silos and start working together to meet the aggressive schedules for early product time-to-market. Although foundries are not the best candidates to partake in silicon validation entirely, the truth is they can help to some extent, especially with design marginalities, because they often have expertise and toolsets not available to design houses.

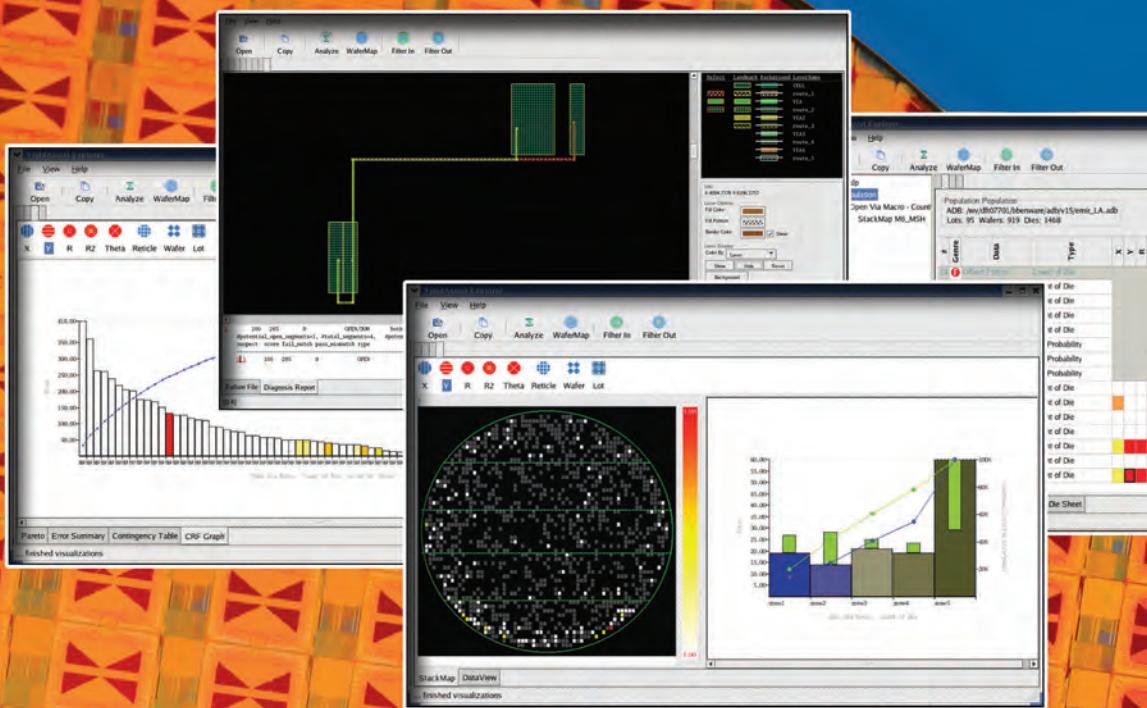

One of the most useful tools for identifying design marginalities in ICs is the laser scanning microscope.

In most modern foundries, tester-based scanning laser microscope diagnostic tools are readily available for device electrical fault analysis. Automatic test equipment docks onto the diagnostic tool to power up the device while failure analysis is performed concurrently.<sup>[20]</sup> In this way, functional issues can be interrogated.<sup>[21-23]</sup> Although the specifications of these tools are capable to apply for design debug, they usually are not utilized for this purpose due to the lack of sufficient design knowledge, such as the expected states at suspected problematic internal nodes. In fact, design centers could leverage this untapped resource for parallel effort in the characterization and root-cause understanding of test failures. This is the first area for collaboration.

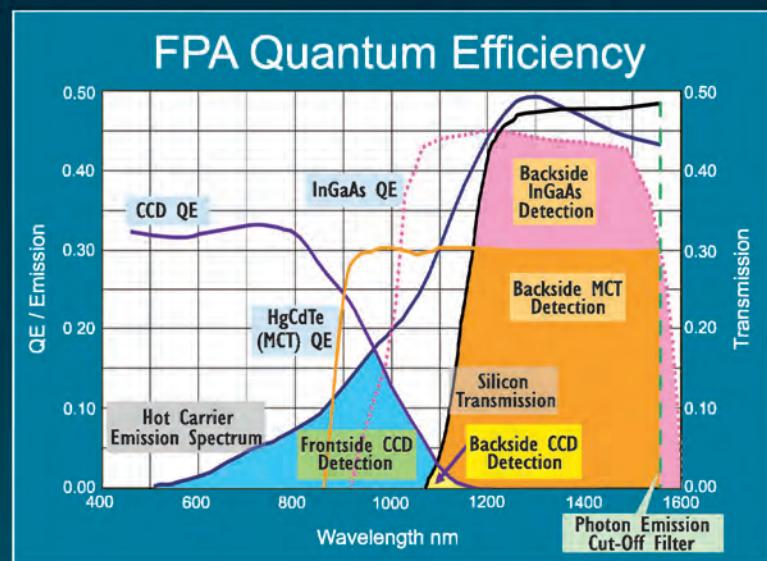

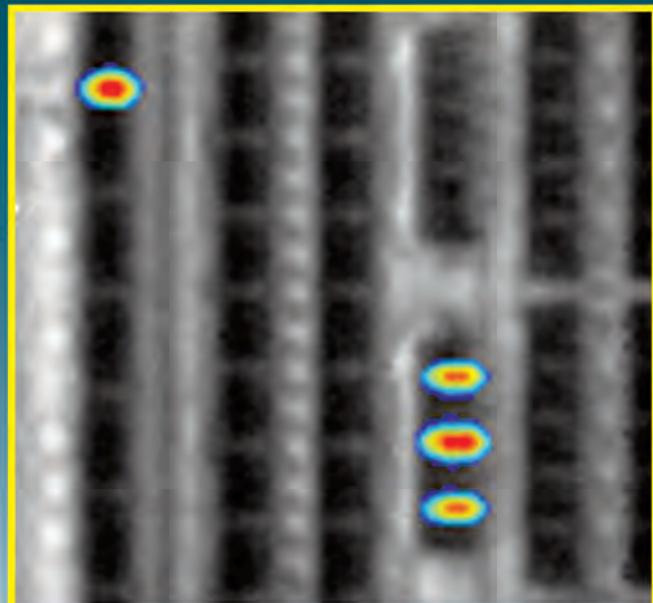

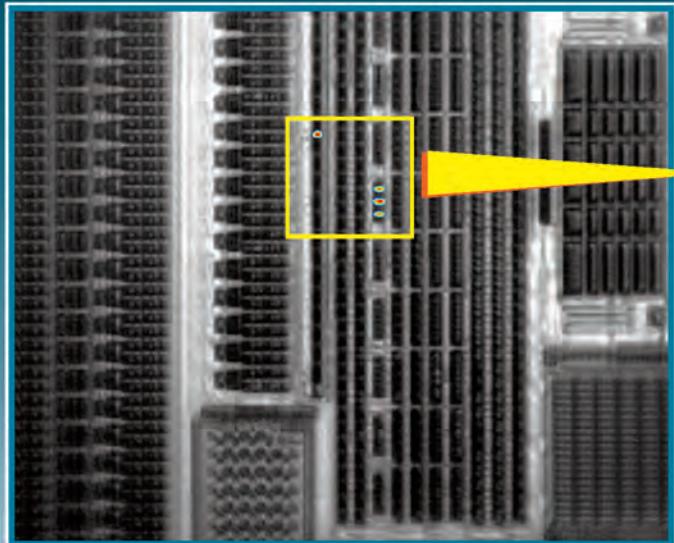

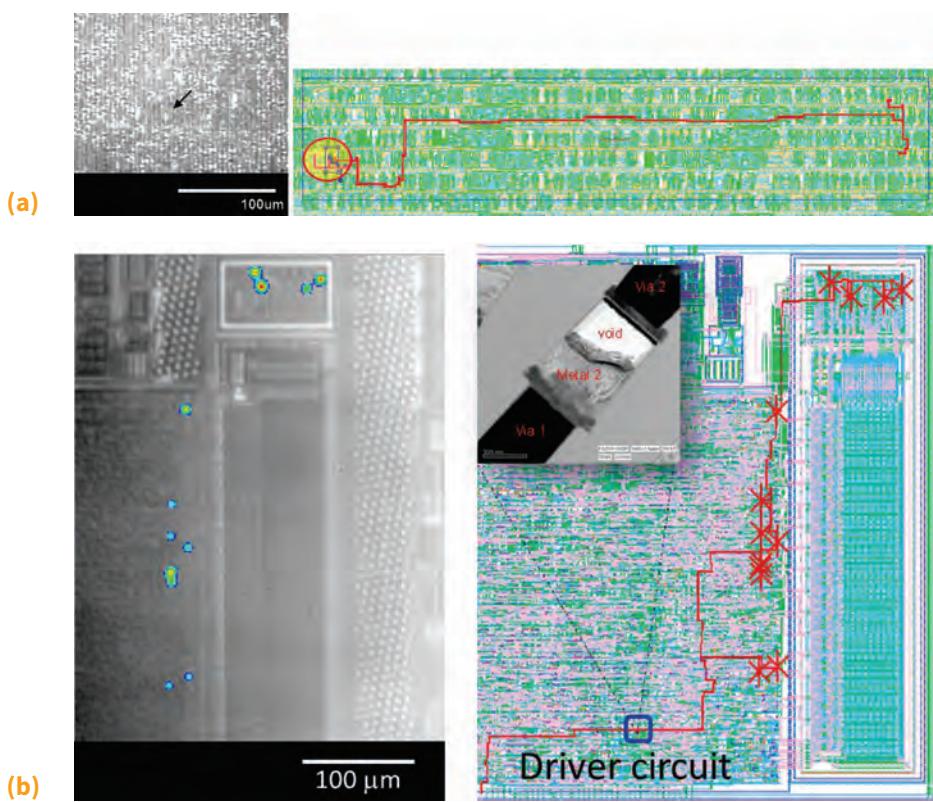

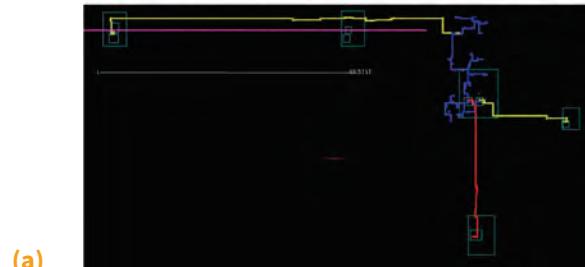

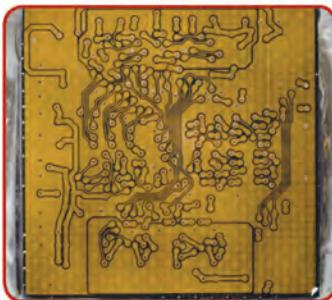

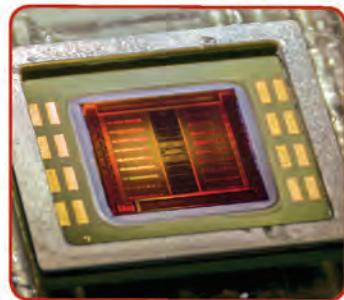

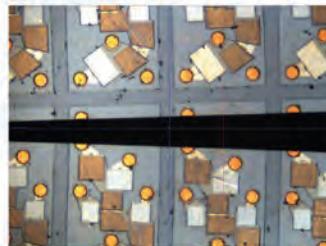

The second opportunity for a foundry to contribute is related to debug on the design schematic to postulate the failure mechanism and to guide subsequent failure analysis steps, after the successful localization of suspected problematic circuitries. Often, design centers are relied upon extensively to accomplish this task. Actually, some basic preliminary analysis can be performed by a foundry to shorten the learning cycle. Figure 1 illustrates two examples of abnormal emission hotspot observations after fault isolation. In both cases, a single failing net connecting the signal locations is able to explain the root cause of the failure. In such scenarios, simple layout analyses suffice. For more complicated failure modes,

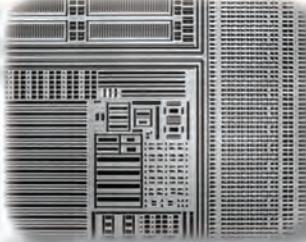

**Fig. 1** Layout trace of suspected failing net connecting (a) single emission hotspot and (b) multiple emission hotspots

such as multiple emission hotspots that are related by multiple connecting nets and parametric-related issues (Fig. 2a and b, respectively), circuit analysis is necessary.

## CIRCUIT ANALYSIS METHODS

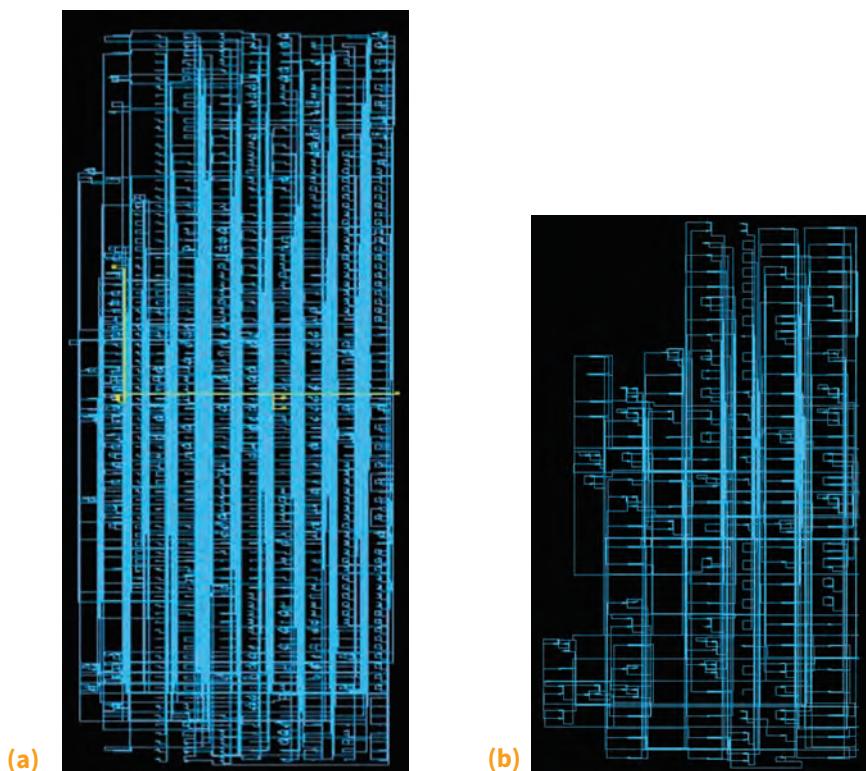

Circuit analysis for failure debug is distinctly different from IC reverse engineering that is commonly performed to detect IP infringements or examine chip security. Reverse engineering involves the use of physical methods to remove the materials layer by layer and acquire high-resolution images at each layer for reconstruction of the layout of the entire IP, or even the chip design, and thereafter generate a schematic. Companies and software tools such as Chipworks and Degate have been well established for this purpose.<sup>[24-27]</sup> Circuit analysis in this article's context refers to examining partial and a much smaller network of circuit components, usually involving one to two levels of fan-in/out net traces that connect the suspected failing instance. In general, this can be accomplished in two ways by the foundry.

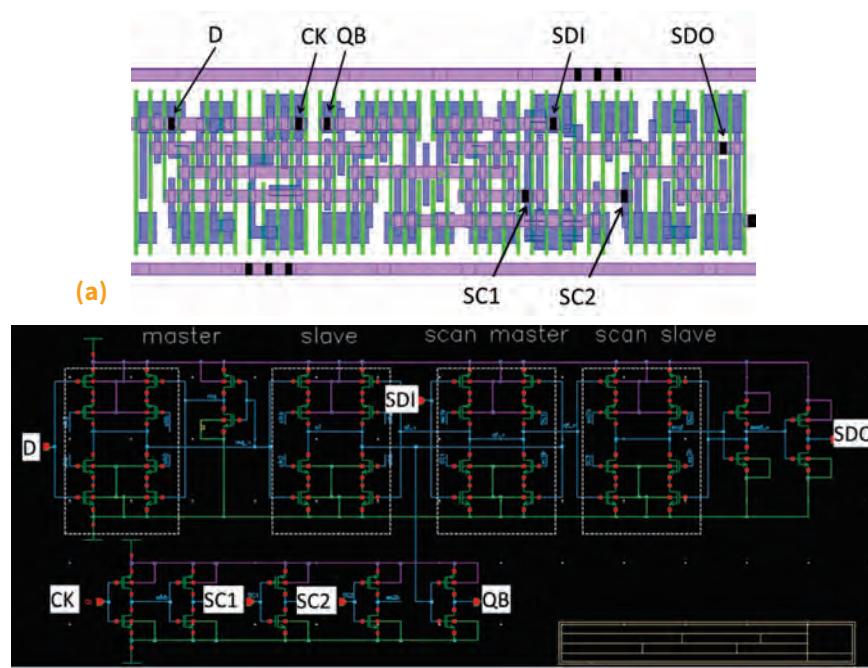

## MANUAL TRACE

The smallest building block to construct a circuit schematic is a basic transistor. From a layout, it can be extracted based on the overlap of polysilicon and diffusion areas. Subsequently, the connecting nets can be traced to map out the relevant netlist. Although this manual process is tedious and time-consuming, there is no sophistication in the knowledge that is required to accomplish this task. It is fundamental to all semiconductor engineers. Figure 3(a) represents the layout of a typical level-sensitive

(continued on page 26)

**Fig. 2** (a) Photon emission micrograph showing hotspots not related by a single trace. (b) Parametric test response discrepancies between processed silicon from two foundries

**Fig. 3** (a) Layout representation and (b) corresponding schematic from manual trace of a typical level-sensitive scan flop

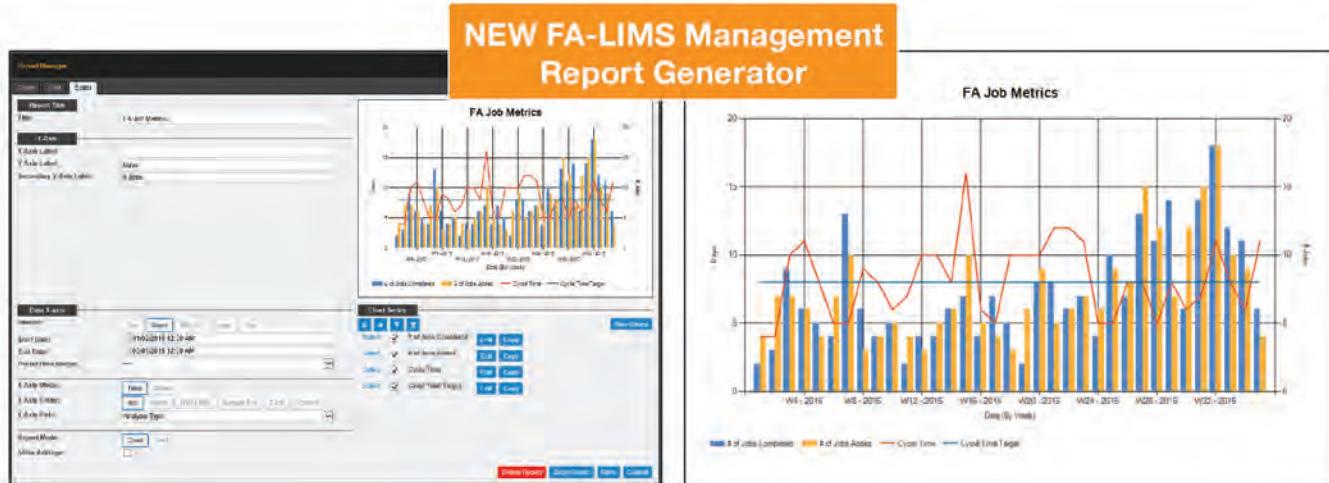

# If You Can't Measure It ...You Can't Manage It

Quartz Laboratory Information Management System for

Failure Analysis and Materials Characterization Labs

## FA-LIMS

### Do You Really Know How Your Lab Is Performing?

- Where are jobs slowing down?

- How much time does a job really take?

- What resources are holding up jobs?

- Who are the best performers?

- Do I need another tool or more staff?

- What job types are being underestimated?

Want a Faster Smarter Lab?

Increase Lab Productivity by 20%<sup>+</sup>

CALL US FOR A DEMO

**QUARTZ IMAGING CORPORATION**

SPECIALIZED SOLUTIONS FOR ELECTRONIC DEVICE LABS

See us at **ISTFA** - Booth #721

Phone: 604-488-3911 • inform2@quartzimaging.com • www.quartzimaging.com

## PRODUCT CIRCUIT VALIDATION AND FAILURE DEBUG

(continued from page 24)

scan design flip-flop. The corresponding schematic that is derived from manual tracing is shown in Fig. 3(b). A circuit analysis can be performed to shed insight on the

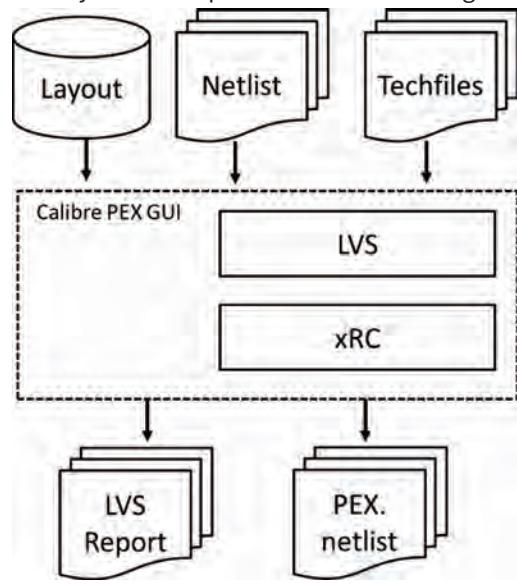

Fig. 4 Block diagram of a standard Calibre PEX flow

bias conditions of the operating modes and the expected performance of the scan cells.

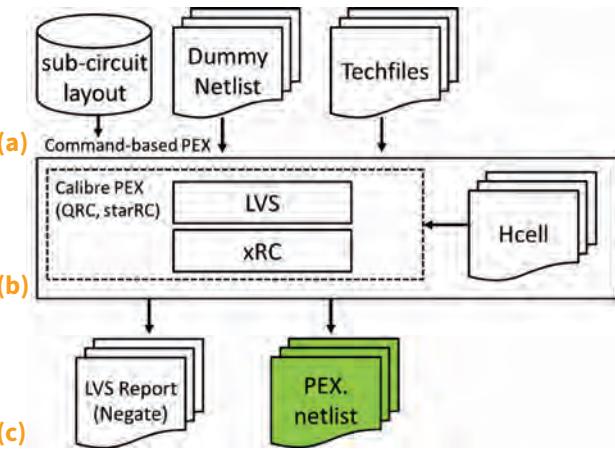

Fig. 5 Modified Calibre PEX flowchart

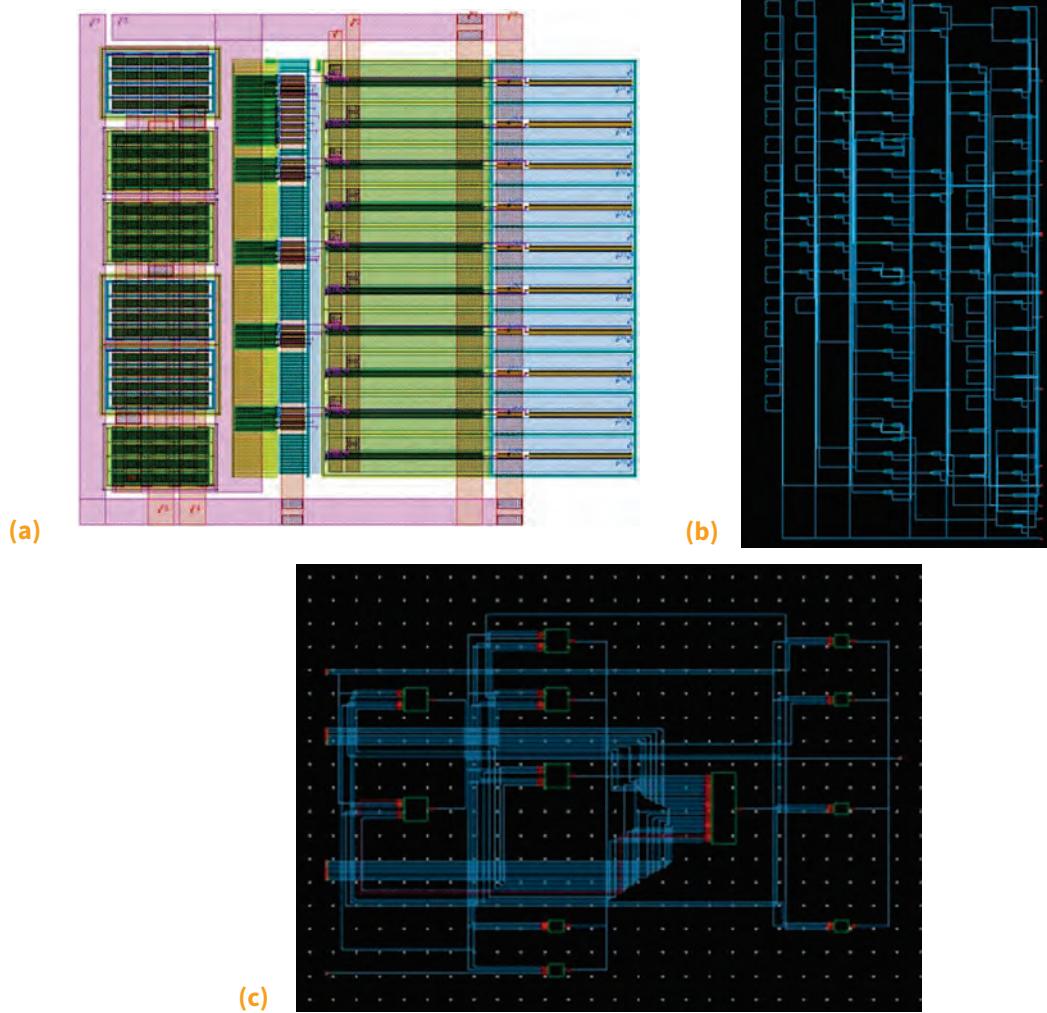

Fig. 6 (a) Layout, (b) extracted flattened transistor netlist, and (c) hierarchical netlist representation of a generic decoder

## PARASITIC EXTRACTION

A more advanced approach to construct a small-area schematic is to leverage parasitic extraction (PEX), which is a standard procedure as part of the design presilicon validation process. The Mentor Graphics Calibre xRC parasitic extractor<sup>[28]</sup> is one example, and it is used in this work. Design layout, netlist, and techfiles are the inputs to the tool. Depending on the environment configuration, it is able to execute layout-versus-schematic (LVS) and PEX at the same time. An LVS report together with the parasitic netlist is generated in the process. The LVS compares the extracted transistor-level netlist against the source netlist for discrepancies, and the parasitic capacitances and resistances data can be stitched to achieve an accurate postlayout simulation for verification/debugging. Figure 4 shows a simplified block diagram workflow. For small-circuit schematic extraction, the LVS and parasitic data are not crucial and could be ignored. Figure 5 presents the

modified workflow. The design layout is truncated, and a dummy netlist is used as the input file, because no source netlist is available. For hierarchical schematic extraction, a hierarchical cell file is required during the PEX process. In general, Cadence QRC<sup>[29]</sup> and Synopsys starRC<sup>[30]</sup> can be used as well.

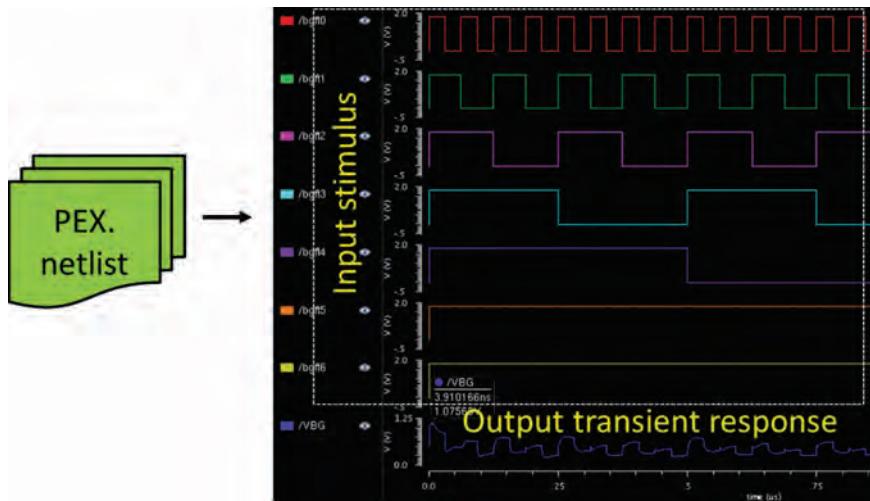

Figures 6(a) to (c) show the layout of a generic decoder, the corresponding extracted flattened transistor-level netlist, and the hierarchical netlist, respectively. With the PEX netlist, further testbench simulations can be performed (Fig. 7). For the purpose of debug, the circuit of interest can be characterized by assigning sources and sinks to emulate the postulated failing conditions (Fig. 8).

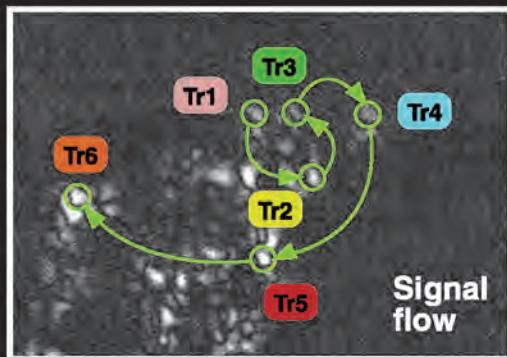

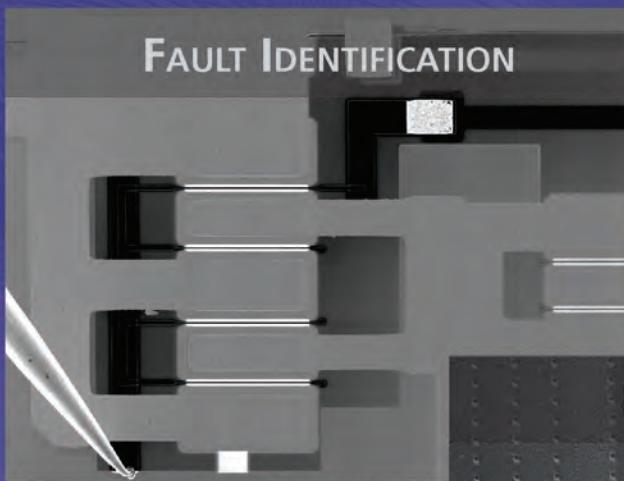

## CIRCUIT ANALYSIS ON ELUSIVE PHOTON EMISSIONS

A systematic failure was encountered on first silicon, and photon emission microscopy isolated the problematic

**Fig. 7** Testbench simulation

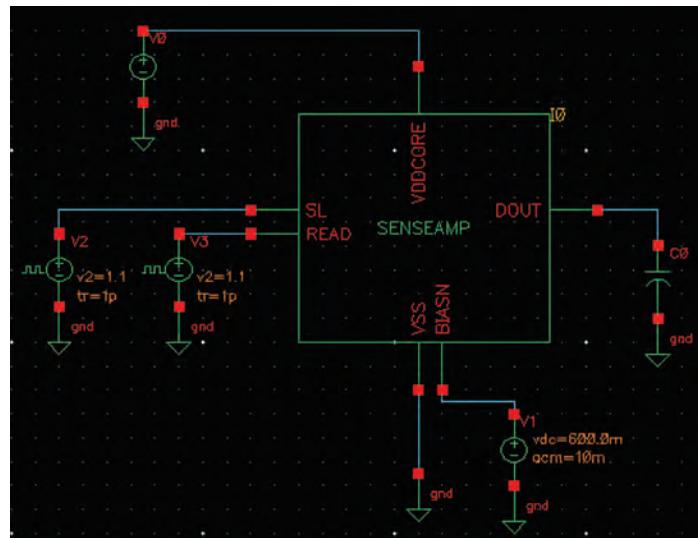

**Fig. 8** Characterization of sense amplifier circuit properties by assigning sources and sinks where appropriate

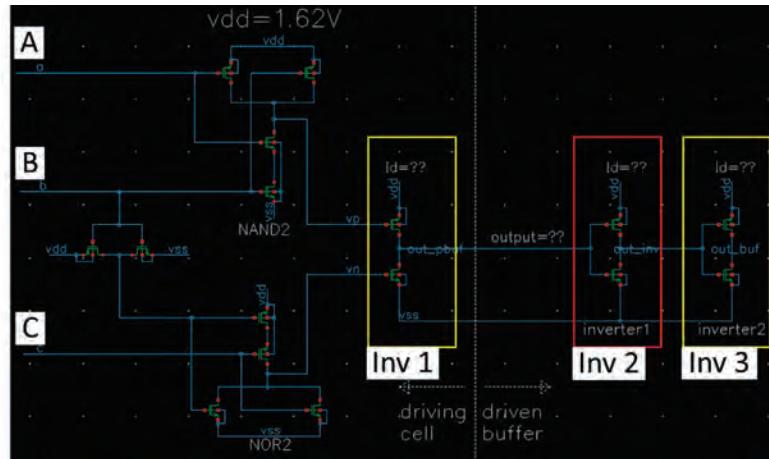

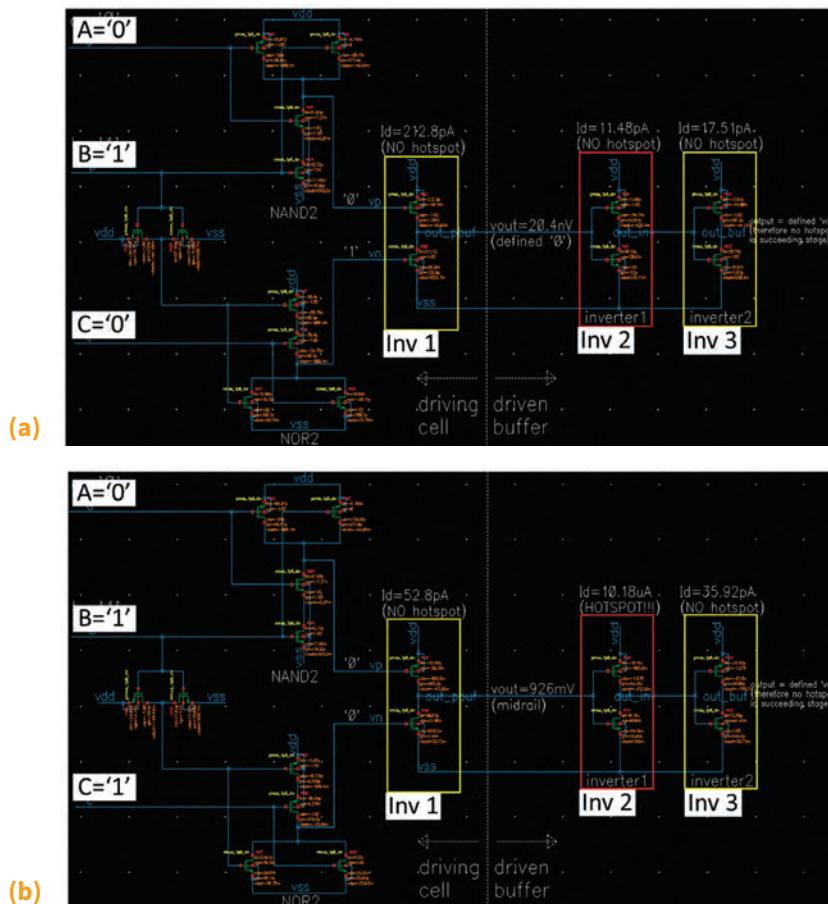

circuitry. Next, the schematic was derived using the manual trace method before circuit analysis ensued. Figure 9 shows a schematic of the circuit under debug (CUD) following guidance from the abnormal photon emissions, which were observed on inverter 2 (Inv 2). Inverter 1 (Inv 1) is the preceding instance, while Inverter 3 (Inv 3) is driven by Inv 2. Consider the case of a defect in Inv 1 leading to saturation in Inv 2; intuitively, the input to Inv 3 will be floating, and emissions should be observed as well. Based on experience, direct physical failure analysis on Inv 1 and

2 is not recommended. The inputs A, B, and C to the combinational logic involved in the CUD were identified and a testbench model was created. In the circuit simulation, various combinations to the inputs were applied, and the crossover current of the three inverters was monitored together with the state of the output driving net from Inv 1. The results of two scenarios are presented in Fig. 10. Figure 10(a) shows that when  $A = 0$ ,  $B = 1$ , and  $C = 0$ , the driving net to Inv 2 is defined as 0, and the drain current is found to be negligible in all three inverters. However,

Fig. 9 Testbench model of CUD. Labels A, B, and C are inputs.

Fig. 10 Drain current of inverters 1 to 3 under input state of (a)  $A = 0$ ,  $B = 1$ ,  $C = 0$  and (b)  $A = 0$ ,  $B = 1$ ,  $C = 1$

when  $A = 0$ ,  $B = 1$ , and  $C = 1$ , as shown by the case in Fig. 10(b), the driving net is found to be stuck at midrail bias. The outcome is a leakage in Inv 2, which explains the photon emission micrograph observation. The issue was identified and a process fix was implemented to resolve the failure. Although all nets in a typical combinational logic circuit should be clearly defined, this is a classic example of a design bug escape in presilicon validation. This is a common phenomenon, especially in complex mixed-signal designs.<sup>[31]</sup>

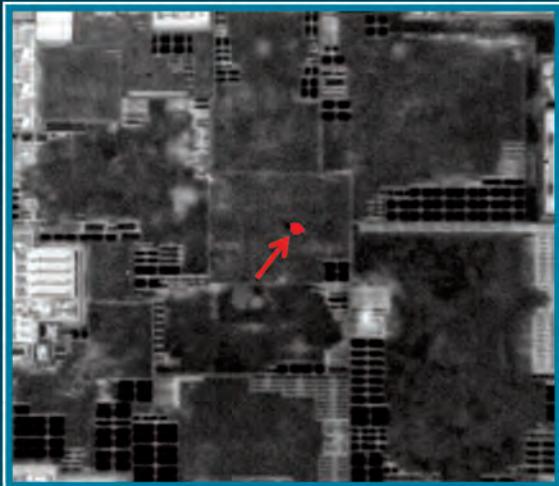

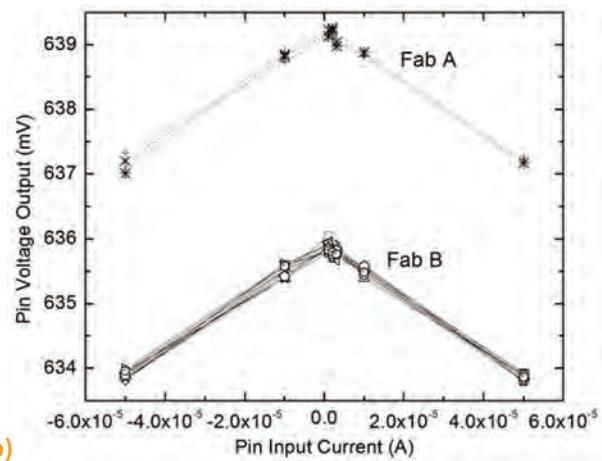

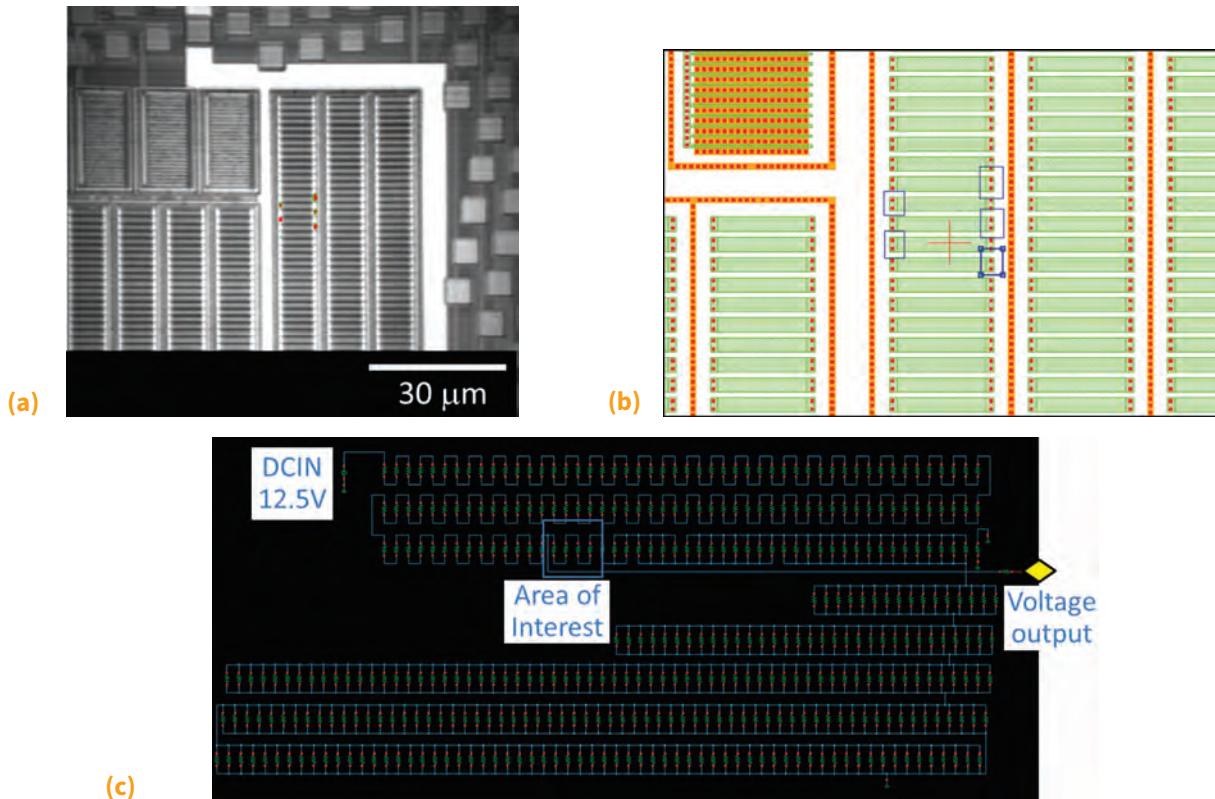

## AYOUT-DESIGN-RELATED PROCESS SENSITIVITY

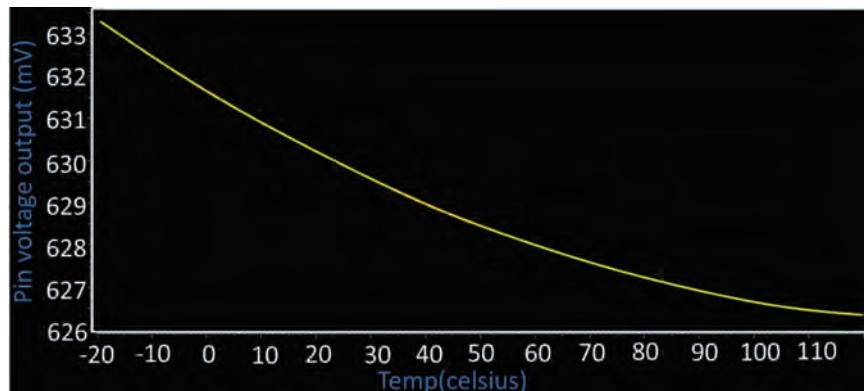

Process transfers across wafer fabrication plants (fabs) within a foundry are common to optimize capacity. A case

of a consistent higher pin voltage output from a silicon-on-chip from the receiving fab, as shown in Fig. 2(b), is discussed. The test response (voltage readout) presents a negative sensitivity to thermal stimulus. Soft defect localization (SDL) is chosen to isolate the critical circuitries. Figure 11(a) shows the SDL signal overlay image. Five signal spots were obtained, and a layout analysis found them to be related to some contacts of poly resistor chains (Fig. 11b). PEX extraction was performed to derive the schematics of the CUD, and the testbench model is shown in Fig. 11(c). The voltage observation pin as well as the signal locations (area of interest) are indicated. The circuit is a simple potential divider. Figure 12 shows the testbench simulation result. The lowering of the voltage output can be explained by the temperature coefficient

**Fig. 11** (a) SDL signal overlay image and (b) corresponding layout indicating five thermally sensitive sites. (c) Testbench model of CUD

**Fig. 12** Testbench simulation on CUD

of resistance of the poly resistors. A secondary analysis of the layout reveals that the lower half of the potential divider has a distinctive routing compared to the upper half, which is a straightforward serpentine of discrete resistors in series. The lower half has a combination of resistors connected in series and in parallel. The SDL signals identify the highest-sensitivity region to be on the serial resistors at the lower-half portion of the divider. It is recommended that the routing be consistent on both halves of the divider to mitigate the process sensitivity for better parametric matching.

## PEX EXTRACTION CHALLENGES

Although it may seem convenient to generate and study the schematic of the CUD using PEX as compared to manual translation, they are complementary in nature; there are cases where PEX is not effective, as substantiated by Fig. 13. Before any PEX execution, the chip layout is clipped to a smaller region that encompasses the CUD. It includes all process layers within the region of interest, thus leading to multiple transistors that are not directly relevant. An example is dummy transistors. Figure 13(a) shows a cluttered, flattened PEX schematic that cannot be easily interpreted for a reasonable analysis. Figure 13(b) shows the schematic following a post-dummy transistors filtering procedure. Although it may appear manageable, the opportune outcome is to achieve a schematic with not more than three stages from the suspected failing location

to minimize the number of intranodes as stimulus and observation points, to facilitate testbench simulations. More work is required to accomplish this, and manual trace is still favored in some situations.

## CONCLUSION

There exists a common goal between design houses and foundries: to constantly strive for faster time-to-production of a new product. To accomplish this, first-silicon success or timely issue resolution is paramount. Foundries have an important role to play above their core competence in addressing potential process concerns. This article reinforces the possibility of foundries to engage in preliminary postsilicon validation activities instead of sole reliance on design houses, specifically on design bugs or design-related marginalities failures that are encountered on first silicon. Methods and examples have been presented to demonstrate how foundries can effectively contribute as an added resource to debug such failures. Although the scope is limited to elementary circuitries, the impact exists. In this way, design houses can zero in on more complicated design issues. It is time to revamp the collaboration between design house and foundry. This is just the beginning.

## REFERENCES

1. N. Hakim: "Introduction to Post-Silicon Validation," 2010, [eecs.wsu.edu/~rliu1/files/PostSiValidation.pdf](http://eecs.wsu.edu/~rliu1/files/PostSiValidation.pdf).

**Fig. 13** PEX netlist based on a random clipped layout (a) in the raw form and (b) after filtering dummy transistors

2. V. Bertacco: "Post-Silicon Debugging for Multi-Core Designs," *Proc. Des. Autom. Conf.*, 2010, pp. 255-58.

3. M. Dehbashi and F. Görschwin: "Automated Post-Silicon Debugging of Design Bugs," *Proc. System, Software, SoC, and Silicon Debug Conf.*, 2011, pp. 67-71.

4. T.C. Luo, E. Leong, M.C.T. Chao, P.A. Fisher, and W.H. Chang: "Mask versus Schematic—An Enhanced Design-Verification Flow for First Silicon Success," *Proc. Int. Test Conf. (ITC)*, 2010, pp. 1-9.

5. K.L. Yeh, C.S. Chang, and J.C. Guo: "Layout-Dependent Effects on High Frequency Performance and Noise of Sub-40 nm Multi-Finger *n*-Channel and *p*-Channel MOSFETs," *Proc. Microwave Symp. Digest (MTT)*, 2012, pp. 1-3.

6. M. Bartley: "The Risks & Rewards of Early Tapeout," *EETimes*, 2014, [eetimes.com/author.asp?section\\_id=36&doc\\_id=1323158](http://eetimes.com/author.asp?section_id=36&doc_id=1323158).

7. C. Edward: "Early Tape-Out: Smart Verification or Expensive Mistake?" *Tech Des. Forum*, 2014, [techdesignforums.com/practice/technique/tape-out-verification-shift-left](http://techdesignforums.com/practice/technique/tape-out-verification-shift-left).

8. J. Keshava, N. Hakim, and C. Prudvi: "Post-Silicon Validation Challenges: How EDA and Academia Can Help," *Proc. Des. Autom. Conf.*, 2010, pp. 3-7.

9. D. Lin, E. Singh, C. Barrett, and S. Mitra: "A Structured Approach to Post-Silicon Validation and Debug Using Symbolic Quick Error Detection," *Proc. Int. Test Conf. (ITC)*, 2015, pp. 1-10.

10. F. Farahmandi, R. Morad, A. Ziv, Z. Nevo, and P. Mishra: "Cost-Effective Analysis of Post-Silicon Functional Coverage Events," *Proc. Des., Autom., Test Eur. Conf. Exhib.*, 2017, pp. 392-97.

11. D. Gizopoulos: *Advances in Electronic Testing: Challenges and Methodologies*, Springer, 2006.

12. B. Eklow and B. Bennetts: "New Techniques for Accessing Embedded Instrumentation: IEEE P1687 (IJTAG)," *Proc. Int. Test Symp.*, 2006, pp. 253-54.

13. B. Vermeulen, T. Waayers, and S.K. Goel: "Core-Based Scan Architecture for Silicon Debug," *Proc. Int. Test Conf. (ITC)*, 2002, pp. 638-47.

14. X. Liu and X. Qiang: *Trace-Based Post-Silicon Validation for VLSI Circuits*, Springer, 2014.

15. D. Bockelman et al.: "Multi-Point Probing on 65 nm Silicon Technology Using Static IREM-Based Methodology," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2005, pp. 40-45.

16. S.Y. Ng et al.: "Laser Voltage Imaging: A New Perspective of Laser Voltage Probing," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2010, pp. 5-13.

17. M.R. Bruce, L.K. Ross, and C.M. Chua: "On Die Logic Analysis through the Backside," *Proc. Int. Phys. Fail. Anal. Integr. Circuits (IPFA)*, 2014, pp. 366-69.

18. W. Lua, G. Ranganathan, V.K. Ravikumar, and A. Phoa: "Combinational Logic Analysis Case Studies Using Laser Voltage Probing," *Proc. Int. Phys. Fail. Anal. Integr. Circuits (IPFA)*, 2016, pp. 51-54.

19. B. Niu, G.M.E. Khoo, Y.C.S. Chen, F. Chapman, D. Bockelman, and T. Tong: "Laser Logic State Imaging," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2014, pp. 65-72.

20. S.H. Goh et al.: "Evolution of Wafer Level Tester-Based Diagnostic System: More than just a Dynamic Electrical Fault Isolation Tool," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2013, pp. 587-93.