FEBRUARY 2017 | VOLUME 19 | ISSUE 1

edfas.org

# ELECTRONIC DEVICE FAILURE ANALYSIS

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

FAILURE ANALYSIS ON SOLDERED BALL Grid Arrays: Part I

TRAPS AND CHARGES

AN EVALUATION OF CORROSION INHIBITORS FOR USE IN ACID DECAPSULATION OF SAMPLES WITH SILVER BOND WIRES

ANADEF 2016 WORKSHOP REPORT

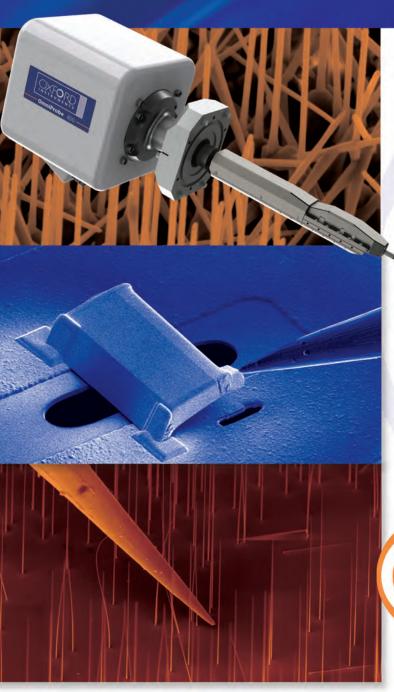

#### **OmniProbe**<sup>®</sup> 400 nanomanipulator

Fast, precise, reliable - and no slip-stick effect

**OmniProbe** 400 delivers efficient nanomanipulation and analysis - even for advanced applications at the nanoscale.

- Unrivalled smooth motion with repeatable positioning

- Precision for sub 100nm structures using closed-loop control

- Efficient omnidirectional motion from millimeters to nanometers

- Compucentric rotation for fast plan-view samples and inverted sample placement

See **OmniProbe** 400 in action moving a 60 nm diameter nanowire www.oxinst.com/60nm

www.oxford-instruments.com/omniprobe

The Business of Science\*

FEBRUARY 2017 | VOLUME 19 | ISSUE 1

edfas.org

# ELECTRONIC DEVICE FAILURE ANALYSIS

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

FAILURE ANALYSIS ON SOLDERED BALL Grid Arrays: Part I

TRAPS AND CHARGES

AN EVALUATION OF CORROSION INHIBITORS FOR USE IN ACID DECAPSULATION OF SAMPLES WITH SILVER BOND WIRES

ANADEF 2016 WORKSHOP REPORT

# ASAP-1° IPS

#### **Interactive Preparation System**

- · Realtime Video Monitor with System Parameters

- Huge Cavity Size Range <0.25mm<sup>2</sup> to >1,600mm<sup>2</sup>

- Automatic Endpoint option

- · Full 5-Axis systems available

- Open System Design allows for fixturing all types and size of part – from surface-mount components, up to Motherboards and Wafers

- Touch-screen control with physical Joystick and Controls Best of Both Worlds

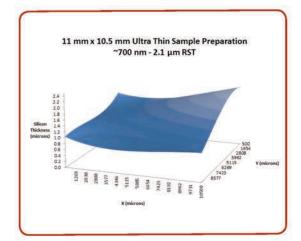

- Meet Current SIL/LVP Requirements (demonstrated 50µm RST +/- 2µm on Flip Chip), and Single Digit RST

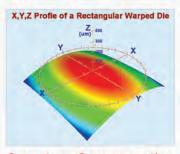

#### MEET 3D & CURVED/WARPED SURFACE CHALLENGES WITH ADVANCED TECHNIQUES

- Auto-Curve and Auto-tilt Setup

- Independent X & Y Axes

- Convex & Concave Surfaces

• Safe and Reliable method to turn complex 3D scenarios into simpler 2D ones

- Reduces dynamic flex of substrate during preparation

- In-situ Hotplate Mode for sample mounting

All Package Types & Sizes • Parts can be decapped, thinned & polished in as little as 45 minutes

#### F-Series Wafer Thickness Measurement System

- Multiple or single-point measurements

- Both 2D and 3D data generated

- Provides Information for achieving final uniformity

Toll Free (US) 1-877-542-0609 Tel: 1-714-542-0608 Fax: 1-714-542-0627 e-mail: info@ultratecusa.com www.ultratecusa.com

# ELECTRONIC DEVICE

#### 4 Failure Analysis on Soldered Ball Grid Arrays: Part I

#### Gert Vogel

New approaches are demonstrated for finding the rootcause failure on ball grid arrays and printed circuit boards.

#### 10 Traps and Charges

#### David Burgess

Learn how to identify, avoid, or eliminate failures caused by mobile ion charges and oxide traps.

#### 14 An Evaluation of Corrosion Inhibitors for Use in Acid Decapsulation of Samples with Silver Bond Wires

#### Kirk A. Martin and Nancy Weavers

An iodic acid solution that is safe, has a very long shelf life, and provides protection for silver bond wires during acid decapsulation is discussed.

#### 22 ANADEF 2016 Workshop Report

Alain Wislez

Read a review of the biennial ANADEF Workshop, which includes prize-winning images from its photo contest.

#### 26 ISTFA 2016 Wrap-Up

A recap of the ISTFA 2016 event includes General Chair Martin Keim's wrap-up, a summary of the Panel Discussion and four User Groups, and a list of the ISTFA Best and Outstanding Papers and Posters.

#### DEPARTMENTS

- **56 ADVERTISERS' INDEX**

- **25 ASM FELLOWS 2016**

- 45 BOARD OF DIRECTORS NEWS Bill Vanderlinde

- **31 CALL FOR PAPERS**

- 52 DIRECTORY OF FA PROVIDERS Rose Ring

- **34 EDFAS AWARDS**

edfas.org

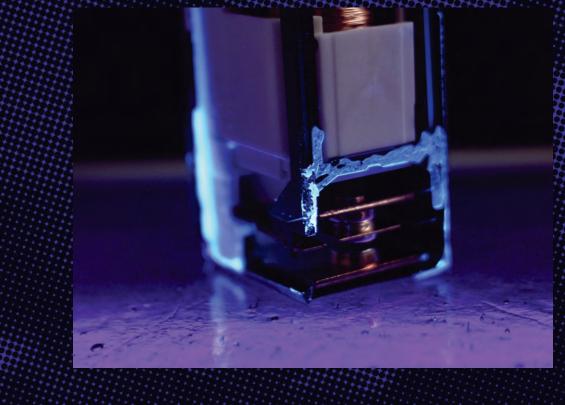

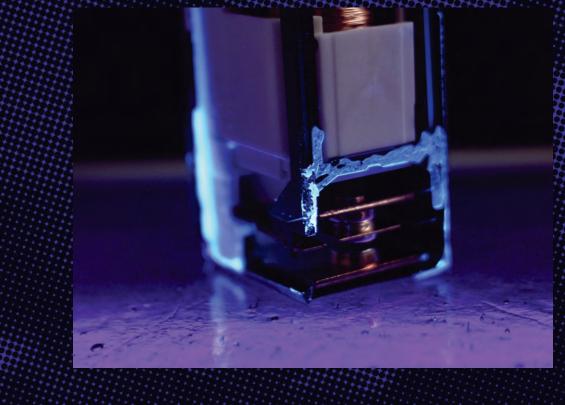

#### **ABOUT THE COVER**

Conformal coat adhered the actuation arm to the lid, preventing the relay from switching. *Photo by Jordan Hendricks, Hi-Rel Laboratories, First Place Winner in Color Images, 2016 EDFAS Photo Contest.*

300 u

#### **Author Guidelines**

Author guidelines and a sample article are available at edfas. org. Potential authors should consult the guidelines for useful information prior to manuscript preparation.

> For the digital edition, log in to edfas.org, click on the "News/Magazines" tab, and select "EDFA Magazine."

#### **54 GUEST COLUMNISTS**

E. Jan Vardaman and Linda Bal

2 GUEST EDITORIAL

Zhiyong Wang, Lee Knauss, and Cheryl Hartfield

- 50 LITERATURE REVIEW Mike Bruce

- **32 PHOTO & VIDEO CONTEST WINNERS**

- 41 PRODUCT NEWS Larry Wagner

- 46 TRAINING CALENDAR Rose Ring

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

#### FEBRUARY 2017 | VOLUME 19 | ISSUE 1

PURPOSE: To provide a technical condensation of information of interest to electronic device failure analysis technicians, engineers, and managers.

**Felix Beaudoin** Editor/Globalfoundries; felix.beaudoin@ globalfoundries.com

Scott D. Henry Publisher

**Mary Anne Fleming** Manager, Technical Journals Kelly Sukol Production Supervisor

**Liz Marguard Managing Editor**

#### OCIATE EDITORS

**Nicholas Antoniou** Revera, Inc. Michael R. Bruce Consultant David L. Burgess Accelerated Analysis **Jiann Min Chin** Advanced Micro Devices Singapore Edward I. Cole, Jr. Sandia National Labs James J. Demarest IBM Szu Huat Goh **Globalfoundries Singapore** Ted Kolasa **Orbital ATK**

Andreas Meyer Globalfoundries

Philippe H.G. Perdu

Rose M. Ring Oorvo, Inc.

Paiboon Tangyunyong Sandia National Labs

David P. Vallett PeakSource Analytical, LLC

E. Jan Vardaman TechSearch International, Inc.

Martin Versen University of Applied Sciences Rosenheim, Germany Lawrence C. Wagner

LWSN Consulting Inc.

#### <u> ARADHIA MASIA</u> www.designbyj.com

#### RELEASE SUBMISSIONS

magazines@asminternational.org Electronic Device Failure Analysis™ (ISSN 1537-0755) is pub-lished quarterly by ASM International", 9639 Kinsman Road, Materials Park, OH 44073; tel: 800.336.5152; website: edfas. org. Copyright© 2017 by ASM International. Receive Electronic Device Failure Analysis as part of your EDFAS membership of \$88 U.S. per year. Non-member subscription rate is \$135 U.S. per year.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by ASM International for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$19 per article is paid directly to CCC, 222 Rosewood Drive, Danvers, MA 01923, USA.

*Electronic Device Failure Analysis* is indexed or abstracted by Compendex, EBSCO, Gale, and ProQuest.

# **GUEST EDITORIAL**

#### STRATEGIC OBJECTIVES FOR EDFAS

Zhiyong Wang, Maxim Integrated, EDFAS President zhiyong.wang@maximintegrated.com

Lee Knauss, IARPA, EDFAS Vice President lee.knauss@iarpa.gov

Cheryl Hartfield, EDFAS Immediate Past President cheryl.hartfield@outlook.com

We just finished our Board of Directors' face-to-face meeting during the 2016 International Symposium for Testing and Failure Analysis (ISTFA) in Fort Worth, Texas, where we defined our EDFAS strategic objectives. As shown below, our strategic objectives are centralized on "strengthen our member resources and grow," with

focuses on three major areas: membership growth, technical excellence, and strategic collaboration and partnership.

#### **EDFAS Strategic Objectives**

Strengthen Our Credential and Grow

#### □ Membership:

- Improve EDFAS brand credential and awareness by communicating through global networks

- Strengthen EDFAS forward-looking "product roadmap" to bring ser-• vices and items of value to members and make them easily accessible through website and social media

- Develop a tailored membership model to encourage "new-career" and international professionals

#### □ Technical Excellence:

- Ensure ISTFA is the premier conference and exhibition for the global electronic failure analysis industry

- Enhance EDFA magazine and desktop reference technical content as the "go-to" sources for global electronic failure analysis industry

- Establish EDFAS technical leadership through education beyond just the means of ISTFA conference

#### □ Strategic Collaborations and Partnership:

• Establish a FA technology roadmap by collaborating with semiconductor and equipment manufacturing institutes

# 600 MHz Lock-in Amplifier

# all you need to generate and analyze your periodic signals

#### The Zurich Instruments UHFLI

- measures amplitude and phase information with high signal-to-noise ratio and high precision

- has a boxcar averager and a scope to work with low-duty cycle signals and to extract specific parts from complex excitation patterns

- has an AWG to generate non-sinusoidal signals and pulses

- 4 analog outputs for fast and simple interfacing with other test equipment

- includes programming interfaces for LabVIEW, MATLAB, C#, Phyton

Let's discuss your application today www.zhinst.com info@zhinst.com Intl. +41 44 515 0410 USA +1 617 765 7263

Your Application. Measured.

Zurich Instruments Gert Vogel, Siemens AG, Digital Factory Division, Control Products, DF CP QM SQA 5 gert.vogel@siemens.com

Ball grid arrays (BGAs) are widely used on complex printed circuit board assemblies (PCBAs). Ball grid arrays are a type of surface-mount package, where it is not possible to directly visually inspect solder connections because they are hidden as an array of small solder balls underneath the devices. X-ray imaging can be used to automatically control the balls regarding soldering faults, but this only provides information about failure types that lead to a deformation of the balls, such as electrical short circuits or voids in the soldered balls.

A detailed analysis of these failures—and also other types of failures that are only accessible by electrical measurements—can usually be conducted only through destructive physical analysis, which involves cross sectioning solder joints. However, BGAs can have more than 1,000 solder balls, and not every type of failure can be identified by taking a cross section.

This article demonstrates new approaches to failure analysis on BGA balls as well as the related failure analysis on printed circuit boards (PCBs).

#### **INTRODUCTION**

Failures of BGAs on PCBAs are primarily related to the solder connection and not to a problem at the silicon level.

There are failures that can be measured electrically, such as short circuits or open circuits in the array of solder balls, as well as failures found by performing an x-ray inspection. For example, voids do not represent an immediate threat but are a long-term quality risk. (A failure is defined as a void percentage of more than 30% of the ball area in the x-ray image, in accordance with IPC-A-610, "Acceptability of Electronic Assemblies.")

Voids such as these in the solder joints of BGAs are very aggravating because they normally cannot be repaired by simply resoldering; even replacing an expensive component with a new one is not always successful. A recourse against the supplier is usually futile because many factors

#### "THIS ARTICLE DEMONSTRATES NEW APPROACHES TO FAILURE ANALYSIS ON BGA BALLS AS WELL AS THE RELATED FAILURE ANALYSIS ON PRINTED CIRCUIT BOARDS (PCBs)."

may be responsible for these types of failures. In most cases, the supplier is right. Even if deep oxidized needle indents in a singular instance can be responsible for voids in BGA balls, the balls are not normally responsible for these types of failures.

#### FAILURE ANALYSIS OF SOLDER JOINTS THAT CANNOT BE VISUALLY INSPECTED

A further complication when analyzing failed BGA balls is that the solder joints cannot be visually inspected. Therefore, obtaining information about the location of an open or short circuit is only possible by making electrical measurements or by performing an x-ray inspection.

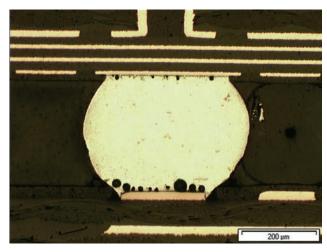

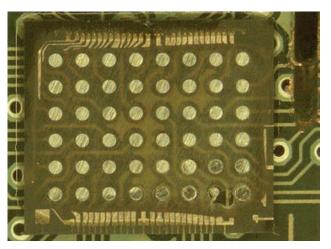

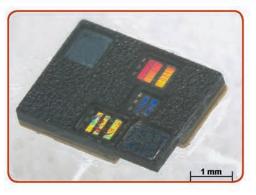

Experience shows that the PCB is predominantly the main source relating to problems involving soldering of BGA balls; however, the solder paste or the soldering process itself can also be responsible for problems. Process problems such as oxygen intrusion during reflow can lead to so-called "champagne voids," which are many small voids on the interface between the solder material and the pad metallization (Fig. 1). The inadvertently added oxygen consumes a high amount of the reducing organic acids from the flux in the solder paste, which was balanced for use under nitrogen atmosphere. If all of the acid is consumed, a web of remaining tin oxide, originating from the grain boundaries of the solder balls, blocks the escape of the gas bubbles that develop. Such a root

EDFAAO (2017) 1:4-8

5

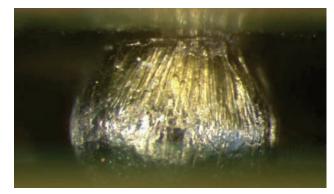

cause can only be revealed by thoroughly controlling all of the parameters of the soldering process. Another clue is the optical appearance of the solder balls after a second

Fig. 1 Cross section through a BGA ball with so-called "champagne voids"

Fig. 2 BGA balls with champagne voids manifest a creased skin after a second reflow.

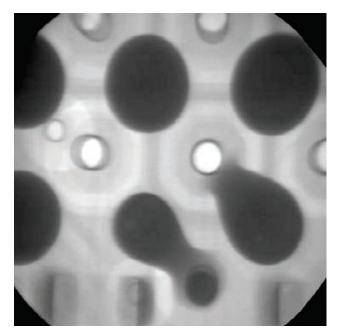

Fig. 3 X-ray image of solder faults at BGA balls

reflow process, which is manifested by a creased skin of tin oxide (Fig. 2).

With several special preparation techniques, many different sources of voiding can be clarified. The goal of the analysis is always to clarify the root cause of the failure so that it can be eliminated in the future. If the root cause has been clearly identified, then an additional benefit is that it may be possible to make a claim against the supplier.

#### ELECTRICAL FAILURES WITH EYE-CATCHING X-RAY OBSERVATIONS

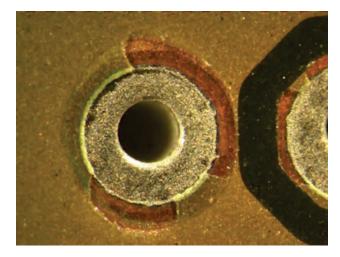

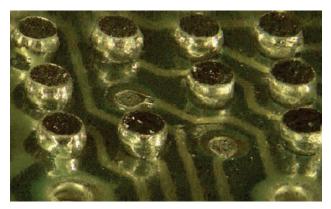

Even if electrical shorts are easily detected by performing an x-ray analysis, the determination of the root cause can still be very complicated. The following example shows very clearly the short circuit between BGA balls and adjacent through-holes in the x-ray image (Fig. 3) as well as in the cross section (Fig. 4); however the root cause must be searched for in the PCB. A bad immersion tin rework underetched the solder resist around openings. It became brittle and flaked off, exposing bare copper that facilitated the flow of liquid solder across the clearance to the adjacent contacts (Fig. 5).

Fig. 4 Cross section of the solder faults from Fig. 3. Short circuits caused by flowing solder as a result of missing solder resist

Fig. 5 Microscopic inspection of the surface of the PCB reveals faulty solder resist. Underetched films broke off, caused by a bad immersion tin rework.

#### PLANE PARALLEL POLISHING OF A BGA TO OBTAIN JUST THE BALLS

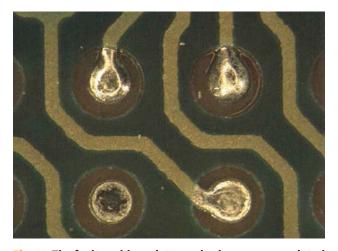

If x-ray analysis and optical microscopy provide no clues for why there is an open circuit between BGA balls and the PCB, if different sizes of BGA balls are visible, or if the BGA is sensitive to coolant spray (intermittent open), then a more drastic approach may be advisable than just a simple cross section through some of the solder joints. If you want to analyze those joints, and something

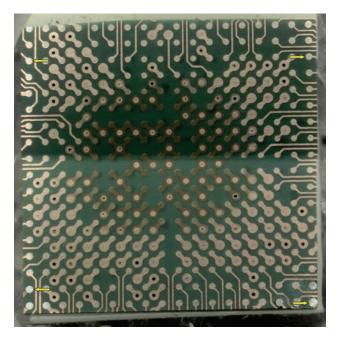

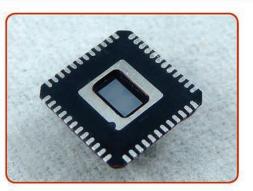

Fig. 6 Removal of the body of the soldered BGA by polishing it down from the top of the BGA. Preparation by plane parallel grinding of the BGA shows some warpage in the soldered BGA. On the left, the PCB of the BGA has already been polished down to the silvery, shining top of the first balls.

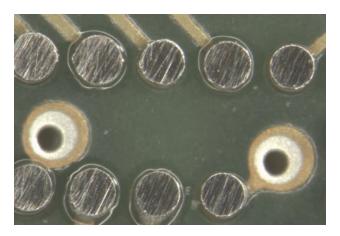

prevents you from looking at them, then remove anything that hinders you. This means grinding and polishing away the complete BGA, leaving only the balls (Fig. 6). After this procedure, one can use a needle to verify whether the solder joint is mechanically stable, and every ball can also be inspected from every direction (Fig. 7). A cross section can still be obtained through the PCB and the solder ball.

The grinding down and polishing of a BGA with an area of several square centimeters is not as complicated as it may appear. It can be done by hand with an accuracy of better than 10  $\mu$ m, because a multitude of copper layers in the BGA help the operator keep in parallel. As soon as the first shiny, silvery small dots appear, one must be very careful, because the last layer of the BGA has been reached. The solder resist around the solder balls cannot be polished away but must be blown off.

The solder balls of the BGA in Fig. 8 manifested different diameters when performing the x-ray inspection. Preparation by grinding down the BGA reveals the root cause: There are no flux residues around the balls having a smaller diameter. This means there is only the solder material of the BGA ball but no printed solder paste, probably because the stencil was dried out and clogged.

#### **TYPICAL ERROR PATTERN: COLD JOINT**

An electrical open circuit was found in the next case. An x-ray examination showed no abnormalities. The BGA was polished down, and just before blowing off the solder resist, a lost solder ball was identified (Fig. 9). Detailed inspection showed that two balls dropped away. The solder pads showed no flux and no solder paste (Fig. 10).

(continued on page 8)

Fig. 7 After exposing all of the balls and blowing away the rest of the solder resist, the balls can be inspected from all sides. No soldering problems were identified.

Fig. 8 In this case, the root cause for varying sizes of the solder balls can easily be seen. Around some balls there are no residues of flux. These balls also have a smaller diameter, which means that no solder paste was printed at these locations.

# Struggling to see photoemissions at low voltages?

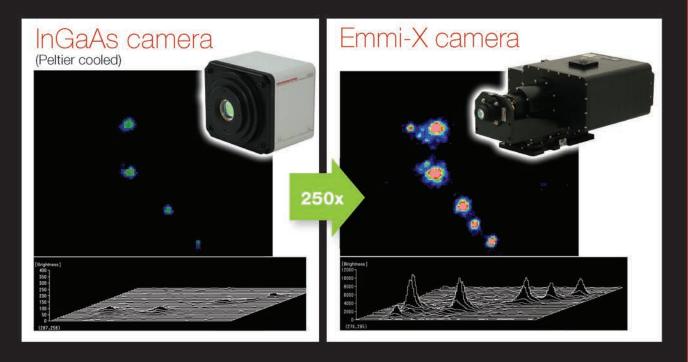

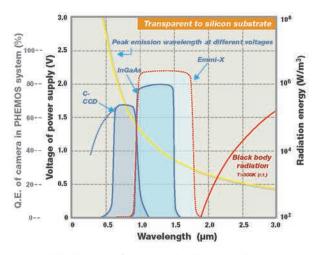

The mobile market demands lower power consumption and Hamamatsu's **Emmi-X** camera delivers unprecedented sensitivity for the low voltage devices of the future. With **250X higher sensitivity** than typical TE cooled InGaAs cameras, the **Emmi-X** will ensure photoemission is your go-to technique for years to come.

Lower Vdd means fainter emissions and at longer wavelengths — requiring extended sensitivity.

Available for these systems: PHEMOS | iPHEMOS | THEMOS | TriPHEMOS

#### Learn more at www.hamamatsu.com or call 858-210-6703

#### FAILURE ANALYSIS ON SOLDERED BALL GRID ARRAYS: PART I (continued from page 6)

Fig. 9 After grinding down the BGA and before blowing away the residue of the solder resist from the bottom of the BGA, it was discovered that one ball had dropped off.

Fig. 10 After blowing away the residue of the solder resist, two missing balls can be seen.

Fig. 11 The faulty solder print can also be seen on a printed pattern with the same geometry next to the defective BGA.

The difference from the BGA in Fig. 8 is that the molten solder ball did not wet the surface of the PCB land. The faulty solder print could also be identified next to the defective BGA on a bare printed pattern without an assembled BGA (Fig. 11). Once again, the root cause of the failure was a dried-out, clogged stencil while printing the solder paste.

#### **SUMMARY**

Based on a number of case studies, it was shown that failure may originate at a number of steps in the manufacturing process, for example, from the solder paste printing process or from the soldering process itself. The stencil printing of the solder paste is often a critical process, but more often, the root cause is faulty PCBs.

Cross sections of soldered BGAs are common for failure analysis. One new approach is presented as an additional method in the course of finding the root cause of failures. Grinding away the corpus of the BGA until the soldered balls are still left on the PCB can provide insight into the failure mechanism.

In the case of perfect solder connections, grinding the PCB from the backside is another approach, which will be discussed in Part II of this article in the May issue of *EDFA*.

#### **ABOUT THE AUTHOR**

**Gert Vogel** studied physics in Stuttgart. He has been with Siemens for more than 30 years. Dr. Vogel was a semiconductor technologist in Siemens' DRAM production in Munich and Regensburg for seven years. He then moved to Siemens

Amberg where, among other topics, he is a specialist in failure analysis of electronic components on printed circuit board assemblies. He led a tutorial, "Avoiding Flex Cracks in Ceramic Capacitors," at ESREF 2015. This was followed by a tutorial, "Creeping Corrosion of Copper on Printed Circuit Board Assemblies," at ESREF 2016.

# UNLOCK THE ANSWERS TO YOUR FAILURE ANALYSIS QUESTIONS WITH

SEM Image of Semiconductor Device

Passive Voltage Contrast (PVC) image of semiconductor device

Backscatter Electron (BSE) image of Wire Bond Cross Section

Electron Beam Induced Current (EBIC) Image of Semiconductor Device SMART FLEXIBLE POWERFUL

#### Questions about...

- Fatigue?

- Corrosion?

- Fracture?

- Delamination?

- Layer Integrity?

- Interfaces?

Come see how JEOL high resolution, analytical Scanning Electron Microscopes and precision Cross Section Polishers help you get answers.

#### Visit jeolusa.com/jeolfa

salesinfo@jeol.com

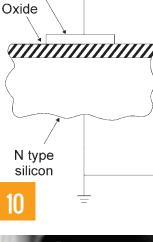

## **TRAPS AND CHARGES**

David Burgess, Accelerated Analysis davidburgess@AcceleratedAnalysis.com

mportant oxide characteristics are skipped over briefly in basic descriptions of MOS operation. Oxide is not even mentioned in descriptions of bipolar devices. In fact, oxide and alternate insulators are critical to semiconductors. Identifying, avoiding, or eliminating inherent problems was, and still is, a major focus for process development.

At the time of the first lunar landing, mobile charges in oxide were an important factor that limited reliability. Today, modern processes and device design have largely eliminated mobile charge failures. However, the mobile charge failure mechanism remains and could reappear any time our defenses lapse. Mobile charge is designated  $Q_m$ .

Oxide traps, however, are more important than ever.  $Q_{f}$ ,  $Q_{it}$ , and  $Q_{ot}$  are designations for three types of oxide traps.

#### **MOBILE IONS**

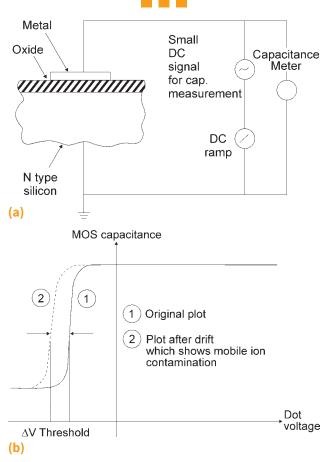

Sodium and potassium ions have a positive charge and move readily in silicon dioxide under influence of an electric field. The electric charge of mobile ions has maximum effect when located near the underlying silicon.

Capacitance-voltage (CV) plotting is used during fabrication to detect and measure the existence of mobile ions. CV plotting is also a good way to understand the behavior of mobile ions in oxide. A simple capacitor is shown in Fig. 1(a), while typical CV plots are shown in Fig. 1(b). The plots show capacitance corresponding to different direct-current voltage applied to the metal dot. At sufficiently negative applied voltage, electrons are repelled from the surface of the silicon, causing a *P*-type inversion layer. Measured capacitance is low because the effective thickness of the capacitor is the oxide thickness plus the inversion layer thickness. At higher applied voltage, the inversion layer disappears. The effective insulator thickness is equal to the oxide thickness alone, and the capacitance increases correspondingly.

Sodium ions have mobility in oxide even at room temperature. In the absence of an applied field, ions in the oxide will spread evenly through the oxide. Mobile ions "TODAY, MODERN PROCESSES AND DEVICE DESIGN HAVE LARGELY ELIMINATED MOBILE CHARGE FAILURES. HOWEVER, THE MOBILE CHARGE FAILURE MECHANISM REMAINS AND COULD REAPPEAR ANY TIME OUR DEFENSES LAPSE."

Fig. 1 (a) Simple capacitor. (b) Two CV plots of metal oxide silicon structure. Plot 1 taken on sample as-fabricated; mobile charge is distributed throughout oxide. Plot 2 taken after high-temperature drift; mobile charge is focused at oxide/silicon interface. diffuse away from regions of high concentration. The like charge of mobile ions causes them to repel each other. The original plot in Fig. 1(b) was taken while mobile charges were evenly distributed. The step increase in capacitance identifies the threshold voltage required to produce the inversion layer.

Plot 2 in Fig. 1(b) was taken after a positive-voltage high-temperature step to drift any positive ions down to the silicon surface. Only a few seconds at 300 °C are required to accumulate near the surface of the silicon. After drifting ions toward the silicon, the capacitor was allowed to cool under bias. Plot 2 was taken while ions were focused near the silicon surface, where their effect is at maximum. A greater negative voltage must be applied to overcome the positive mobile ion and cause inversion. The threshold voltage has shifted.

The difference in threshold voltage is a measure of mobile ions present. The randomly uniform distribution of mobile ions can be restored by baking without bias at 300 °C for a few seconds or at 125 °C for 24 h.

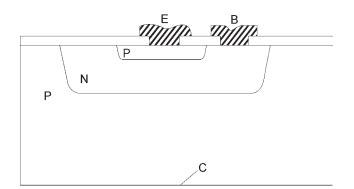

#### MOBILE IONS IN PNP TRANSISTORS

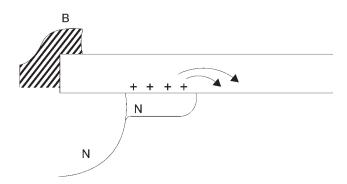

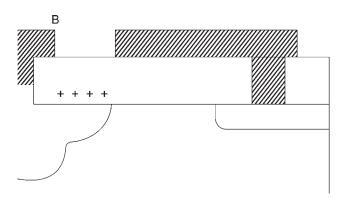

Failures of very early *PNP* devices illustrate more characteristics of mobile ions. Actions to avoid *PNP* failures verify our conclusions. Figure 2 is a cross section of a 1970 transistor. In normal operation, the base is biased at a voltage higher than the collector voltage. An electric "fringe" field exists in the oxide above the base/collection junction. Mobile ions in the vicinity move away from the base toward the collector. In time, mobile ions concentrated at the silicon surface attract electrons and invert the silicon surface. As a result, the base spreads out into the previous collector area. The electric fringe field moves to the new junction and expands the inverse further. Figure 3 shows the expanded base. At this point, transistor parameters do not change drastically. The new junction adds a small amount of leakage current. Breakdown of

the new diode is usually higher than the original collector/base diode.

However, the inversion ultimately reaches the edge of the silicon chip. Current flows directly from base to collector through the inversion layer. The edge of the chip provides a leakage path. The collector/base I/V characteristic becomes a classic channel current.

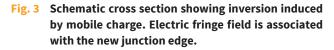

A first attempt to avoid channel current was to add a  $P^+$  "channel stop." The idea was that the P ring would be too highly doped to allow inversion. In fact, the edge of the heavily doped P ring did invert. The depth of the inversion was so shallow that electrons simply tunneled through<sup>[1]</sup> (Fig. 4).

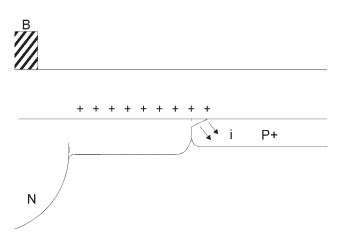

A successful remedy was to add a metal ring contacted to the *P* ring. The metal and the silicon directly below are at the same voltage. No electric field exists under the ring. Lacking an electric field, the inversion cannot expand under the metal (Fig. 5).

Fig. 4 Schematic cross section showing tunnel current at edge of ineffective *P*<sup>+</sup> channel stop. The inversion cannot proceed, but the leakage path is established.

#### **MOBILE IONS IN ICs**

The following three corrective actions have made such failures rare:

- Cleaner fabrication minimizes mobile ions.

- Processes include phosphorus glass, which "getters" mobile ions. That is, phosphorus glass effectively locks mobile ions safely away from critical oxide.

- Nitride and metal elements act as barriers to mobile charge. Mobile ions cannot penetrate nitride films.

While steps to avoid IC failure are overwhelmingly successful, it is clear that under unique conditions, mobile ions could cause fatal leakage between isolated *n*-wells or threshold shifts in MOS transistors. Mobile ions must be considered a possible cause for bake-recoverable failures. Look for cracks or misalignments that defeat steps to control mobile charge.

#### **OXIDE-TRAPPED CHARGES**

Three categories of charges are associated with traps or oxide defects:

- *Fixed charge*  $(Q_{f})$ : Incomplete oxidation of silicon leaves a positive charge by failures of very early PNP devices approximately 2 nm above the interface to the silicon. Crystal structure makes the fixed charge lower for 100 silicon material than for 111 material. (Q, was labeled  $Q_{ss}$  in early publications.)<sup>[2]</sup>

- Interface charge  $(Q_{it})$ :  $Q_{it}$  is similar to  $Q_{f}$  if located at the • interface to the silicon, and it can be either positive or negative. Electrons and hydrogen can be trapped at these locations. This charge is sensitive to oxidation details, such as temperature and the presence of oxygen. A hydrogen anneal is often used to minimize charge. Process variations to achieve a high-k dielectric, such as addition of hydrogen and hafnium, also affect  $Q_{it}$ .

- *Trapped oxide charge (Q*<sub>ot</sub>): A broken silicon-oxygen bond can occur anywhere in an oxide film. Traps can be created during oxide growth or at any later time. High-energy events such as radiation, plasma processing, hot carrier injection, and simple oxide current can create oxide traps, which present a preferred path for oxide current. Thus, traps are involved in timedependent dielectric breakdown and electrostatic discharge failure.

Fig. 5 Schematic cross section showing successful channel stop. Electric field is eliminated by guard ring.

many ways to failure or degradation due to an excess of oxide traps. Gate leakage or threshold changes can cause function failures, timing failures, and many other failures.

Identifying the cause of failure depends on identifying exactly what failed, when it failed, and under what circumstances. A considerable amount of data may be required to conclude the cause of failure. More than a single failure is required to accomplish this.

Plasma etching is known to damage oxides.<sup>[3]</sup> Voltage is built up due to unequal exchange of positive and negative ions. The degree of charging is a function of processing variables. Circuit layout is critical. Layout controls the exposure of gate oxides to damaging discharge current. The key to analysis may be the observation that damaged oxide is, or is not, connected to material that acts as an antenna for charge. Design rules limit the amount of poly or metal allowed to act as an antenna for gate oxide.[4] Diodes are often added solely to protect gate oxide by shunting plasma-induced current away from vulnerable oxide.

Gate oxides are degraded by current flow from any cause. Excess voltage can be caused by circuit configuration or external probing. In addition, excess voltage can be caused by reactive ion etch during decapsulation for failure analysis.

#### REFERENCES

- 1. A.S. Grove: "The Origin of Channel Currents Associated with P<sup>+</sup> Regions in Silicon," IEEE Trans. Electron Dev., June 1965, 12(12), pp. 619-26.

- 2. B. Deal et al.: "Characteristics of Surface State Charge (Q<sub>e</sub>) of Thermally Oxidized Silicon," J. Electrochem. Soc., 1967, pp. 266-77.

- 3. L. Pantisano et al.: "Experimental Approach to Evaluate Plasma Damage in MNOS and PMOS Devices," Int. Reliab. Phys. Symp. (IRPS), 1999, pp. 375-80.

# ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 19 NO.

#### **OXIDE FAILURE**

As suggested previously, gate oxides are susceptible in

4. K.P. Cheung: Plasma Charging Damage, Springer, 2012, p. 316.

#### **ABOUT THE AUTHOR**

**David Burgess** is a failure analyst and reliability engineer. He developed techniques and taught in those areas at Fairchild Semiconductor and Hewlett-Packard. He is the founder of Accelerated Analysis, a manufacturer and distributor of specialty failure analysis tools. David is the co-author of *Wafer Failure Analysis for Yield Enhancement*. A graduate of Rensselaer Polytechnic Institute and San Jose State University, he is a member of EDFAS and has served on various ISTFA committees. David is a Senior Life Member of IEEE and was General Chairman of the 1983 International Reliability Physics Symposium (IRPS).

# **I** NOTEWORTHY NEWS

#### **2017 FIB/SEM WORKSHOP**

The tenth annual FIB/SEM Workshop will be held on **Thursday, March 2, 2017,** at the National Institute of Standards and Technology (NIST) in Gaithersburg, Md. It features a full day of technical content and plenty of opportunities for informal discussion with your FIB colleagues.

For more information, contact the following organizers: Nabil Bassim, bassimn@mcmaster.ca; Ken Livi, klivi@jhu.edu; or Keana Scott, keana.scott@nist.gov.

# **I** NOTEWORTHY NEWS

#### **2017 IRPS CONFERENCE**

The IEEE International Reliability Physics Symposium's (IRPS) annual conference will be held **April 2 to 6, 2017,** at the Hyatt Regency in Monterey, Calif.

The IRPS technical program includes technical sessions, keynote and invited talks on emerging issues, tutorials, workshops, an evening poster session, a year-in-review seminar, panel discussions, and equipment demonstrations. Special attention is given to the reliability of advanced CMOS scaling, new materials introduction, new processes or integration strategies, and/or fundamentally new device architectures. Attendees returning from the IRPS will be better equipped to solve critical reliability problems and develop effective qualification procedures that affect their companies' bottom line.

The IRPS Conference is sponsored by the IEEE Reliability Society and IEEE Electron Device Society. For more information, visit the IRPS website at irps.org.

#### AN EVALUATION OF CORROSION INHIBITORS FOR USE IN ACID DECAPSULATION OF SAMPLES WITH SILVER BOND WIRES

Kirk A. Martin, RKD Engineering Nancy Weavers, Left Coast Instruments kirk@rkdengineering.com or nweavers@lcinst.com

#### BACKGROUND

In previous literature on decapsulation of integrated circuits with silver bond wires,<sup>[1]</sup> a 2.2% Lugol's solution (potassium iodide and iodine in water) was mixed in bulk with fuming nitric acid and used as an etchant in both hand decapsulation and with an automatic decapsulation system. The freshly mixed etchant worked well, but after 30 to 45 min, the bond pull strength dropped off, reaching zero at 2 h. The bond pull tests showed peak forces at approximately the 1:30 mix ratio, with the pull force dropping off at both higher and lower ratios.

The mechanism of protecting the silver wires has been assumed to be the result of a coating of silver iodide that forms on the wire.<sup>[1]</sup> This could either be the result of a reaction between silver nitrate and potassium iodide:

$\begin{array}{l} \mathsf{Ag}+\mathsf{2HNO}_3 \rightarrow \mathsf{AgNO}_3(\mathsf{s})+\mathsf{NO}_2(\mathsf{g})+\mathsf{H}_2\mathsf{O}:\!\mathsf{AgNO}_3+\\ \mathsf{KI} \rightarrow \mathsf{KNO}_3(\mathsf{aq})+\mathsf{AgI}(\mathsf{s}) \end{array}$

or the direct reaction between silver nitrate and iodine:

$2AgNO_3(s) + I_2 + 4H^+ \rightarrow 2AgI(s) + 2NO_2(g) + 2H_2O$

Both cases will produce a porous silver iodide coating that is not very soluble in fuming nitric acid. It should be noted that silver nitrate is only slightly soluble in fuming nitric acid but is highly soluble in water. Because water is produced during the digestion of the encapsulant, it may be locally in high concentrations.

The characterization of the iodine transport and reaction on the wire is necessary to optimize reagent concentrations at these active surfaces and to stabilize the process results in relationship to the age of the etchant. An etchant is needed, or a means of mixing at the point of use, that provides optimum and repeatable wire protection without shelf life concerns.

#### "IT MAY BE POSSIBLE TO OBTAIN BETTER WIRE PROTECTION WITH LOWER IODINE CONCENTRATION, BUT THE REACTIVITY WITH THE WIRES AS SHOWN AT HIGHER CONCENTRATIONS MAY INDICATE A VERY LIMITED PROCESS RANGE AND LACK OF STABILITY."

introduces iodine as iodide (I<sup>-</sup>) and tri-iodide (I<sub>3</sub><sup>-</sup>). The introduced iodine will react with the nitric acid, creating additional species. The possibilities are dissolved elemental iodine created by the oxidization of I<sub>3</sub><sup>-</sup>, iodide (I<sup>-</sup>), and iodate (IO<sub>3</sub><sup>-</sup>). Upon contact between the fuming nitric acid and the Lugol's solution, I<sub>3</sub><sup>-</sup> oxidizes to I<sub>2</sub>, which is further oxidized to iodic acid:

$I_2 + 10HNO_3 \rightarrow 2HIO_3 + 10NO_2 + 4H_2O_3$

A second reaction takes place between the iodic acid and iodide:

$IO_3^- + 5I^- + 6H^+ \rightarrow 3I_2 + 3H_2O$

The iodine created is oxidized to iodic acid, and the cycle continues until the only species left is iodate. At the mix ratios in Ref 1, iodate will be at a concentration of 0.438 mol/L of acid, and  $NO_2$  will be five times higher. This produces enough  $NO_2$  to generate a definite yellow color to the mixture. The reactions also create a lot of water, approximately 4 mol of water for each mole of iodine. In total, the water content of the Lugol's solution and the water from the reactions will add approximately 4% water to the etchant.

Some literature indicates that the solubility of iodine in nitric acid is fairly high.<sup>[2,3]</sup> One paper suggests that (continued on page 16)

#### **IODINE TRANSPORT**

The addition of Lugol's solution to fuming nitric acid

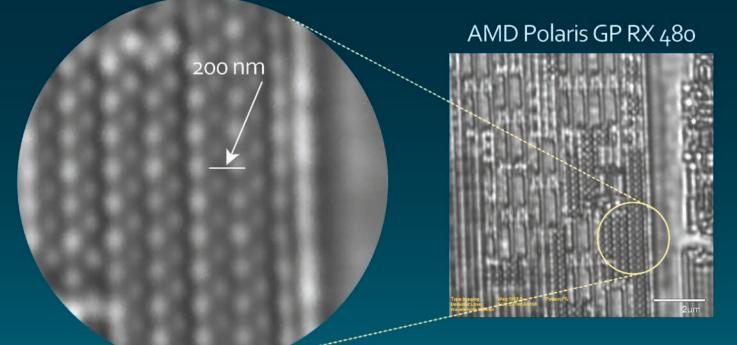

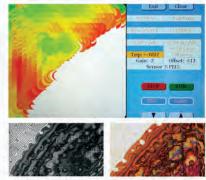

# SEMICAPS ARSIL Super Resolution Images

All images taken by 1064 nm laser

14 nm device with spacing between nodes of about 200 nm

SEMICAPS 3000 Inverted Tester-Docked System

Your Solutions Partner

www.semicaps.com

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 19 NO.

#### AN EVALUATION OF CORROSION INHIBITORS FOR USE IN ACID DECAPSULATION (continued from page 14)

iodine concentrations of up to 0.024 mol/L are possible for 100% nitric acid.<sup>[2]</sup> The same authors indicate that it can take many days for nitric acid/iodine solution to equilibrate in concentration. This observation makes prior data, such as in Ref 3, questionable in absolute values but valid for relative values. The long time required to dissolve iodine has been observed in our work, with some solutions requiring several days for all of the iodine to go into solution. This long time frame indicates that little iodine is actually dissolved in the nitric acid during the 2 h shelf life observed in Ref 1, eliminating direct dissolution as a transport mechanism.

The oxidization of iodine to iodate by concentrated nitric acid is well known, as is the reaction of iodide with iodate in an acidic environment. This indicates iodate as the primary iodine-transport mechanism shortly after the etchant is mixed. Because the solubility of iodic acid in 98% nitric acid is very low, the iodic acid may be transported as a suspension as well as a solute.

#### EVALUATION OF ETCHANT COMPOSITION OVER TIME

To create a process that is not subject to solution shelf life considerations, it is necessary to understand what changes over time in the etchant described in Ref 1. This was done by mixing according to Ref 1 and evaluating the solution over time intervals for contained iodate and iodine. The iodine test does not discriminate between dissolved or suspended particles. Because iodine evaporates from iodine and tri-iodide solutions, a fresh 2.2% Lugol's solution was made up immediately before performing the tests. One milliliter of the solution was placed into a graduated cylinder, and 30 mL of 98% fuming nitric acid was added. The mixture turned yellow and was stirred manually for a few seconds. Samples were periodically taken as close to the surface as possible. When sampled, two samples were taken. One was diluted to 1 molar HNO<sub>3</sub>, and the other was diluted and neutralized to a pH of approximately 7.5. The neutralized samples were titrated to determine iodine content. The diluted samples were evaluated for iodate. The concentration difference required the use of different solutions for the titrations. A high concentration of thiosulfate was required for the iodate samples, and a very low concentration for the iodine samples. Any undissolved iodate entrained with the sample will dissolve in the water used for dilution. This may match the characteristics of the etchant as it is pumped from the source bottle. Because the iodate precipitates and settles, less will be entrained in the etchant.

The starting assay indicated that all iodine introduced is converted to iodate. The assay also indicated no detectable dissolved iodine. Over time, as the iodate precipitate settled to the bottom of the acid mix, the concentration of iodate decreased, while dissolved iodine remained undetectable. After 12 h, the acid solution was clear, and little iodate was detected. After hours, small amounts of iodine were detected. This indicates that the presence of iodate is a function of time and the settling rate of the iodic acid. Because the iodate is not soluble in fuming nitric acid, it readily precipitates out, producing the limited life observed in Ref 1. The iodine-transporting compound does not decrease in efficacy; it simply settles out.

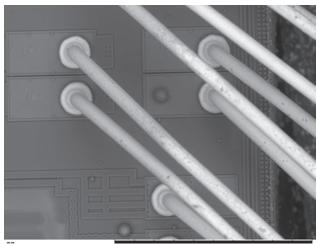

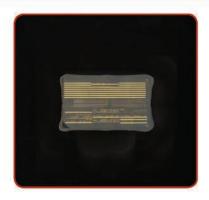

## EVALUATION OF WIRE PROTECTION FROM DISSOLVED IODINE

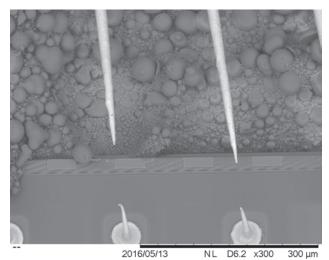

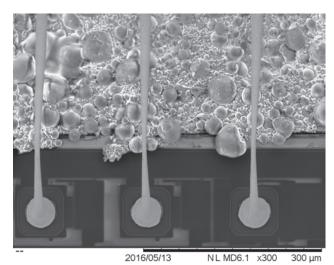

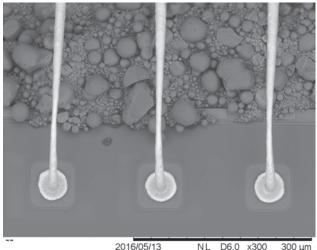

To determine if dissolved iodine could contribute to the preservation of silver bond wires, a test was devised that used only dissolved iodine. A volume of 70% nitric acid was placed on a stirring hot plate set at 30 °C. An excess of iodine was added, and the acid was left for approximately 36 h. The solution took a strong red-orange color. This solution was used as the inhibitor source for etching four parts with an I53 connected to an Elite Etch-Cu. (The I53, manufactured by RKD Engineering Corp., is a patent-pending syringe pump configured to introduce small quantities of a corrosion inhibitor into the acid stream of an automatic decapsulation system. The Elite Etch-Cu, model 7100, is an automatic dual-acid decapsulator manufactured by RKD Engineering Corp.) The first part was etched for 120 s with a ratio of 20:1. The etch results indicated that a longer etch time was needed. The remaining three parts were etched for 150 s with acid-to-inhibitor mix ratios of 15:1, 25:1, and 30:1. The results are shown in Fig. 1 to 3.

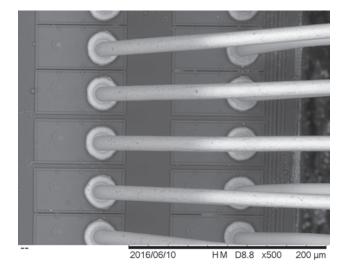

Fig. 1 150 s etch with 15:1

Over a 2-to-1 range in iodine concentration, the process changes from elimination of wires to varying degrees of wire thinning. It can be seen that iodine dissolved in 70% nitric acid provides some protection at the mix ratios tried. The measured iodine content of the solution was 0.00372 mol/L. This results in iodine concentrations of 0.00025, 0.00015, and 0.00012 mol/L at the mix ratios used above. It may be possible to obtain better wire protection with lower iodine concentration, but the reactivity with the wires as shown at higher concentrations may indicate a very limited process range and lack of stability.

#### **EVALUATION OF WIRE PROTECTION** FROM DISSOLVED IODATE

A saturated solution was made of potassium iodate in deionized water. The concentration is highly temperature dependent but was approximately 0.3 normal. This is approximately 30 times the measured iodate

Table 1

Silver wire decapsulation recipe

| Etch temperature | 30 °C                         |

|------------------|-------------------------------|

| Heat-up time     | 120 s                         |

| Etch time        | 120 s                         |

| Etch volume      | 3 mL/min                      |

| Rinse time       | 0 s                           |

| Etch mode        | Pulsed HNO <sub>3</sub> + INH |

| Ratio            | 30:1 (acid:inhibitor)         |

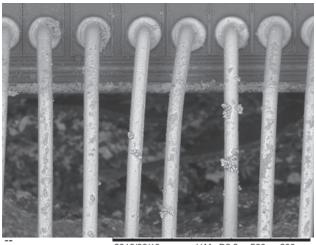

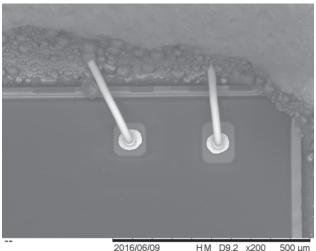

concentration established in the evaluation of the etchant used in Ref 1. This solution was used as the corrosioninhibitor source for an I53 connected to an Elite Etch-Cu. The samples decapsulated were the same type as used in Ref 1, but a slightly different recipe was used, as shown in Table 1.

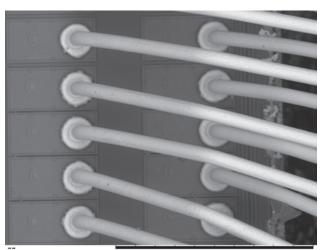

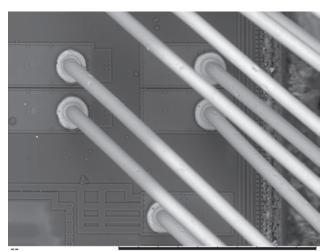

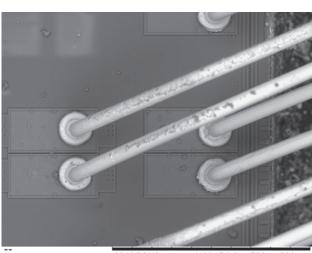

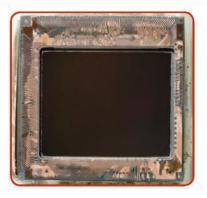

As can be seen from Fig. 4, this process effectively prevents wire damage from the fuming nitric acid used for decapsulation.

Approximately 72 h later, the same solution and recipe was used to decapsulate another sample. The results shown in Fig. 5 demonstrate that the solution is stable over this time frame. The premixed etchant used in Ref 1 lost effectiveness in less than 2 h.

Due to the sensitivity of the solution concentration to temperature and its limited solubility at any temperature, solutions were investigated using iodic acid. In addition to much higher possible concentrations in water, iodic acid is somewhat soluble in dilute nitric acid, depending on the HNO, concentration. The addition of nitric acid to the solution reduces the amount of water introduced, minimizing metal loss and increasing the efficacy of the etchant. Two solutions were made up. The first solution

2016/06/08 HM D8.6 x500 200 um

Fig. 3 150 s etch with 30:1

Fig. 4 Etched with potassium iodate

edfas.org

Fig. 2 150 s etch with 25:1

2016/06/10 HM D8.8 x500 200 μm

2016/06/10 HM D9.1 x500 200 μm

Fig. 5 Same recipe 72 h after Fig. 4

2016/06/10 HM D8.9 x500 200 μm

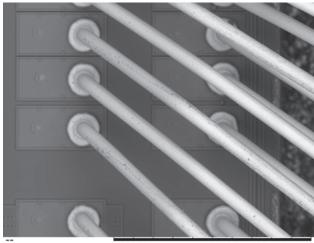

Fig. 6 20:1 iodic acid

Fig. 9 20:1 iodic acid in dilute nitric acid

2016/06/10 HM D8.9 x500 200 μm

2016/06/10 HM D9.1 x500 200 μm

19

D8.9 x500 200 um

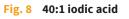

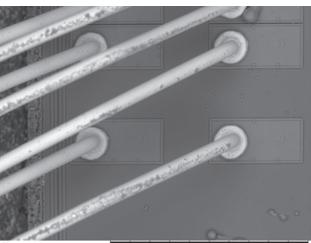

Fig. 11 40:1 iodic acid in dilute nitric acid

2016/06/10

D8.9 x500 200 um

Fig. 12 Etched using iodic acid at 50 °C

Fig. 13 Etched using iodic acid with 360 s etch time

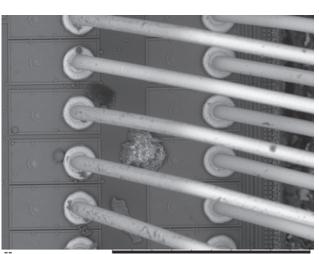

was 0.3 normal HIO<sub>3</sub> in water. The second was 0.3 normal HIO<sub>3</sub> in 50% HNO<sub>3</sub>. The etch results, at different fuming nitric acid to corrosion-inhibitor mix ratios, are shown in Fig. 6 through 11.

All electron micrograph images were taken with the Hitachi High Technologies TM-3030Plus tabletop scanning electron microscope. No sample preparation was used, to negate the possibility of any sample-preparation artifacts. As can be seen, there is no detectable difference in wire quality. Along with the increasing amount of etch debris with lower amounts of introduced water was a corresponding increase in the size of the etched cavity. As the encapsulant-removal rate increases, so does the debris load of the etchant and the greater the amount left on the wires and die surface.

#### DISCUSSION

The data presented in Ref 1 indicate a fairly narrow range of process parameters that produce undamaged silver bond wires. Bond pull strengths dropped with increasing etch time, higher and lower mix ratios, higher etch temperatures, and greater age of the premixed etchant.

Using a corrosion inhibitor that was directly injected into the fuming nitric acid flow path in an automatic decapsulator significantly increases the available range of process parameters. Varying the etchant-to-inhibitor ratio by a factor of 2 produced no detectable difference in wire quality. The inhibitor has a nearly infinite shelf life.

Initial evaluations of effects from increased etch times and higher etch temperatures indicate significant increases in the useful range of these parameters as well, as shown in Fig. 12 and 13.

All of the parts shown in the figures use silver alloy wire. It has been found in additional evaluations that pure silver wires require a higher-concentration inhibitor solution. An iodic acid solution at 1.0 M concentration reproduces the results shown with pure silver bond wires.

#### CONCLUSION

Silver bond wires can be protected from damage during acid decapsulation by the injection of a corrosion inhibitor into the acid stream. The use of a 0.3 M iodic acid solution provides protection of silver alloy wires over a wide range of process parameters, including etch time, etch temperature, and the amount of inhibitor injected. Additionally, a 1.0 M iodic acid solution will provide the same protection for pure silver wires. This solution also has a very long shelf life and is relatively safe.

Mixing corrosion inhibitors directly into the bulk acid used for decapsulation may produce similar results, but the mixture has a limited lifetime due to solubility limitations and slow reactions between the etchant and inhibitor. Bulk mixing may also precipitate materials that will damage the fluid pump inside an automatic acid decapsulator. "On the fly" mixing of the inhibitor and etchant requires a mixture lifetime of only a few seconds to be effective, and there are no particulate concerns.

#### REFERENCES

- 1. M. Lefevre, E. Noraz, and D. Veychard: "Repeatable Method for Automated Decapsulation of Silver Alloy Wire Packages," *Proc. 41st Int. Symp. Test. Fail. Anal. (ISTFA)*, Nov. 1-5, 2015.

- 2. A.I. Lutsyk et al.: "Solubility of Iodine in the System Water-Nitric Acid," *Russ. J. Appl. Chem.*, July 2004, 77(7), pp. 1195-97.

- 3. J.S. Carter: J. Chem. Soc., 1925, 127, pp. 2861-65.

#### **ABOUT THE AUTHORS**

**Kirk Martin** has 40 years of experience in designing and building specialized equipment for all aspects of the semiconductor industry, from crystal growth through final test and failure analysis. In 2005, he became a founder of RKD Engineering, which designs and builds equipment for semiconductor failure analysis and sample preparation. Kirk has patents in the fields of sample preparation, chemical vapor generation, fluid handling, and electrostatic discharge detection and mitigation. His previous positions include Vice President at Nisene Technology Group; Director of Advanced Products at Texas Materials Labs, a manufacturer of specialty semiconductor materials; and Vice President at Automated Technology, Inc., a manufacturer of front-end test and measurement systems.

**Nancy Weavers** has 30 years of experience in applications in the semiconductor and test equipment industries. She started at National Semiconductor in 1982. In 2006, she became the Chief Executive Officer of Left Coast Instruments, a semiconductor test equipment and electron microscope imaging sales and marketing company. She sits on the Board of Advisors for the San Joaquin Delta College Electron Microscopy Program. Previously, she was a Vice President at Nisene Technology Group.

# **I** NOTEWORTHY NEWS

#### **MICROSCOPY & MICROANALYSIS 2017 MEETING**

The Microscopy & Microanalysis (M&M) 2017 meeting will be held **Aug. 6 to 10, 2017,** in St. Louis, MO, with a theme of "Anniversaries." The Scientific Program features the latest advances in the biological, physical, and analytical sciences as well as techniques and instrumentation along with special anniversary lectures. A special symposium will celebrate 50 years of atom probe tomography. Complementing the program is one of the largest exhibitions of microscopy and microanalysis instrumentation and resources in the world. Educational opportunities include a variety of Sunday short courses, tutorials, evening vendor tutorials, pre-meeting workshops, and in-week intensive workshops. The opening reception offers an opportunity to meet new people in the field and renew old acquaintances, and the Monday morning Plenary Session features showcase talks from outstanding researchers as well as recognition of the major Society and Meeting award winners. There will be other important awards conferred during the meeting, including daily poster awards to highlight the best student posters in instrumentation and techniques as well as biological and physical applications of microscopy and microanalysis.

M&M is co-sponsored by the Microscopy Society of America and the Microanalysis Society and, for the first time, by the International Field Emission Society. For more information, visit microscopy.org/MandM/2017.

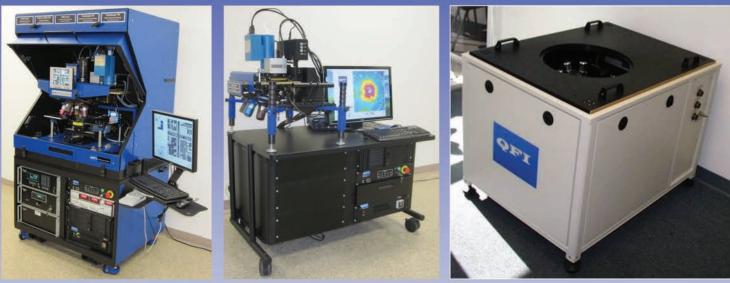

# **Design Flexibility** A Core Component of QFI Microscopes

Integrated Probe Stations 200/300 mm

Portable LabWalker<sup>™</sup>

ATE-Docking

#### Application requirements drive configuration decisions.

QuantumScope<sup>™</sup> failure analysis microscopes and InfraScope<sup>™</sup> temperature measurement microscopes are available in a variety of configurations. Flexibility has always been a core design principle at QFI. We understand the need to consider both current and projected applications when establishing the appropriate capability set for any analytical equipment. QFI systems are generally compatible with field upgrade to address changing requirements. We invite you to discuss your specific analytical needs. Please let us know how we can assist you via the contact information listed below.

**Quantum Focus Instruments Corporation**

2385 La Mirada Drive • Vista CA 92081 Phone: +1 (760) 599-1122 Fax: +1 (760) 599-1242 e-mail: sales@quantumfocus.com http://www.quantumfocus.com

### ANADEF 2016 WORKSHOP REPORT

Alain Wislez, ANADEF Workshop President, Thales Group alain.wislez@thalesgroup.com

#### The ANADEF 2016 Workshop attendees

he 15th ANADEF Workshop (failure analysis and failure mechanisms of electronic components) was held June 7 to 10, 2016, at the sea resort Les Tuquets in Seignosse, France, near the famous surfing spot of Hossegor on the Atlantic Ocean. The workshop is organized by ANADEF, the French Failure Analysis Society, which meets biennially in a unique, friendly, and intergenerational spirit. Training and sharing of experiences

and skills on solved and unsolved failure analysis (FA) case studies, techniques, and tools as well as trends and the future of FA are presented in a warm, friendly, and informal but professional manner that includes extended after-dinner exchanges.

As a record-setting year, the ANADEF Workshop gathered 152 people from a wide industrial and university

The sea resort Les Tuquets

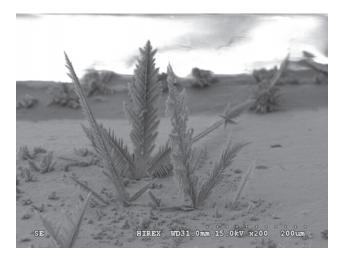

"Oasis Cristallin," first prize in the ANADEF Photo Contest

background: IC manufacturers, energy, aeronautics, space, defense, automotive, tool and equipment suppliers, and FA lab providers. Almost 50% of the attendees were newcomers, which presented an opportunity to enlarge the ANADEF network.

30 µm

Grand. = 292 X

Signal A = SE2

Date :27 Aout 2015

EHT = 10.00 kV

WD = 10.7 mm

Date :27 Aout 2015

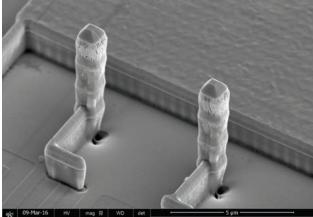

"Iron Hand," second prize in the ANADEF Photo Contest

202 09-Mar-16 HV mag @ WD det 203 3:30:30 PM 5.00 kV 10 000 x 3.9 mm TLC

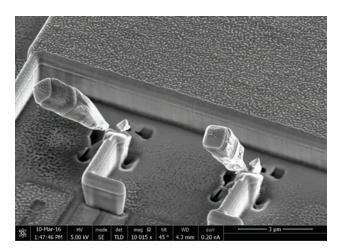

"Twin Towers 1 and 2," third prize in the ANADEF Photo Contest Because most attendees were beginning and midcareer technical scientists involved in FA who wished to advance their careers, a professional education program was again provided for technicians, engineers, and postgraduates. The program was given by industry experts, all of whom were ANADEF members.

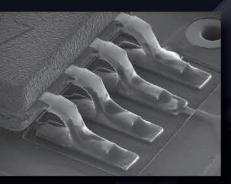

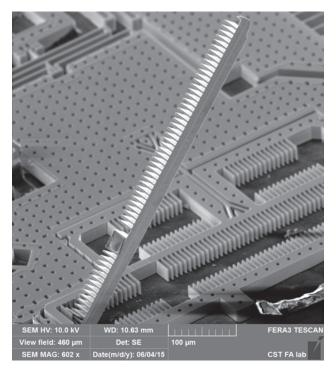

"Stairway to Heaven," technical prize in the ANADEF Photo Contest

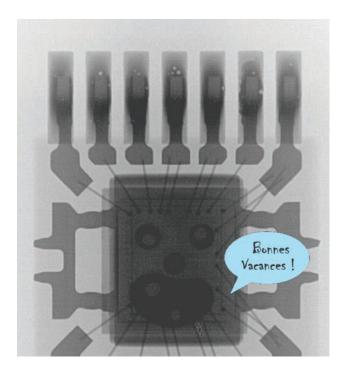

"Happy X-Rays," unusual prize in the ANADEF Photo Contest

The 2016 FA courses addressed many of the usual topics, such as packaging, power electronics components, highly integrated circuits, physical-defect-based reliability approach, printed circuit board and bonding processes, as well as many new topics, such as optical, light-emitting diodes, and laser components; thermal characterization; how to manage dynamic reliability; and helpful tools for FA.

A high-quality FA photo contest created competition among all the participants. More than 60 photos were submitted for the photo contest, with six being selected as the winners.

The sea resort Les Tuquets and its environment as well as the organization of the event widely favored exchanges between attendees at all levels, even after the days' programs. This was a unique opportunity to share FA expertise and to deepen the discussion of topics presented during the sessions as well as business, technical trends, and so on.

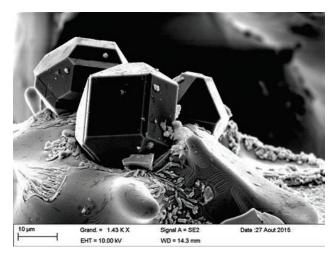

"Single Crystals of Silicon," aesthetics prize in the ANADEF Photo Contest

Since 1988, the ANADEF event has been held biennially. The next workshop is scheduled for 2018. For more information, visit anadef.org.

**CONTINUED FROM**

PAGE 2

# GUEST EDITORIAL

- Partner with other international conferences and organizations to co-host or share contents

- Seek opportunities with educational institutes such as universities to extend EDFAS education offers

What does EDFAS mean to you as a member? Where do you derive the most value? To grow our members, first and foremost, we need to strengthen EDFAS brand promises globally, then we need to strengthen our "product roadmap" and make it accessible to our members. Finally, we need to reform our membership structure to accommodate emerging needs, such as new-career and international electronic failure analysis professionals.

When we joined EDFAS many years ago, it was the technical content that attracted us. Today, we are still going strong! Stronger than ever, as demonstrated by many years of successful ISTFA conferences and exhibitions, with many years of effort from many individuals under the leadership of the EDFAS Board of Directors. We need to keep it going! We need to sustain our technical excellence by ensuring the premier status of ISTFA, enhancing *EDFA* magazine and *Microelectronic Failure Analysis Desk Reference* impact, and establishing an educational model beyond what we are already getting through ISTFA. collaborate and partner with many related organizations and institutes, such as semiconductor and equipment manufacturing companies, to establish a strong electronic device failure analysis technology roadmap, co-host or share technical content with other international conferences or organizations, and seek additional educational opportunities through partnership with educational institutes such as universities. By empowering these, we can make an impact on the industry we reside in, build a knowledge pipeline benefitting our members, and, most

importantly, we can grow organically as a Society.

EDFAS is built on volunteerism. The EDFAS Board fully understands we cannot achieve our strategic objectives without help from our volunteers. We would like to use this opportunity to ask each of you today to look inside yourself and find how you can best promote your profession and do a little bit of good for your professional society. We need volunteers on all EDFAS committees to keep our strategic objectives on track. We need volunteers for the local chapters. We need authors to write papers to present at the conference. There is no end to the ways you can get involved, and we challenge you to find those ways and get involved! We look forward to seeing you at ISTFA 2017 in Pasadena, California.

How can we do this? We need to reach out; we need to

25

# Image: ASM FELLOWS 2016

#### **EDFAS MEMBERS NAMED ASM FELLOWS**

The Electronic Device Failure Analysis Society (EDFAS) is proud to announce that three of its members were named to ASM International's 2016 Class of Fellows: **Lee Knauss, Philippe Perdu,** and **David Vallett.** In 1969, ASM established the Fellow of the Society honor to provide recognition to members for their distinguished contributions to materials science and engineering and to develop a broad-based forum of technical and professional leaders to serve as advisors to the Society. This year's awards were presented at ASM's annual Awards Dinner on Tuesday, October 25, 2016, in Salt Lake City during Materials Science & Technology 2016.

**Dr. Lee Knauss, FASM,** Chief, Technology Transition, IARPA, Washington, D.C., was recognized "for the development and advancement of magnetic current imaging fault isolation techniques used in microelectronics failure analysis."

**Dr. Philippe Perdu, FASM,** Microelectronic Senior Expert, CNES, Toulouse, France, was recognized "for outstanding leadership and technical contributions toward the development of novel defect localization and failure analysis techniques applied to microelectronics and microsystems devices."

**Mr. David Vallett, FASM,** Owner, PeakSource Analytical LLC, Fairfax, Vt., was recognized "for sustained outstanding technical contributions, leadership, dissemination of knowledge, and education in microelectronic IC fault

isolation and failure analysis technology and magnetic imaging applications, and for articulating and publicizing major analytical technology hurdles and challenges throughout the industry."

EDFAS congratulates these gentlemen on achieving the distinguished honor of ASM Fellow. They join Larry Wagner (2010), Ed Cole (2013), Bill Vanderlinde (2014), and Tom Moore (2015) as EDFAS members selected for this honor.

EDFAS Vice President Lee Knauss, FASM (left), was onsite to receive his award during MS&T16 in Salt Lake City. He was congratulated by Ed Cole, FASM (middle), and EDFAS President Zhiyong Wang (right).

#### **ISTFA 2016–WOW!**

Martin Keim, ISTFA 2016 General Chair Mentor Graphics Corporation Martin\_Keim@Mentor.com

EDFAS luncheon and general membership meeting

STFA, our yearly International Symposium for Testing and Failure Analysis, came to a close in Fort Worth, Texas, on November 10, 2016, and what a great Symposium it was! ISTFA grew on all fronts—bigger and better than in previous years. With 795 total attendees, counting the Symposium and Expo, ISTFA 2016 had more participants than ISTFA 2015 and enjoyed an 11% growth over ISTFA 2014. Also, the Expo grew in numbers, with 75 companies displaying their goods and services, including three companies that had never exhibited at ISTFA. To keep up with the demand, twelve booth spaces were added in the middle of the year; nonetheless, the Expo floor was sold out. The Technical Program grew larger, too, with a third parallel track added to the Monday afternoon schedule.

#### **BIGGER, YES, BUT BETTER?**

Growing numbers are only one indication of a good Symposium. Growing numbers show that you valued your experience in previous years, so you came back. The numbers show that ISTFA is a good place to publish your work and that companies on the Expo floor value coming to ISTFA, meeting you, establishing new contacts, and setting up or closing business deals. But how did ISTFA 2016 do on the quality of the program compared to previous years, so you will plan on attending ISTFA in 2017? Well, as General Chair I am naturally somewhat biased in saying that we did well, offering you a great, high-quality program. There is evidence to back up this statement. During ISTFA, I took every opportunity to talk with you, the attendees, about what you thought of this year's event, of ISTFA in general, and what we can do better. The feedback I received was overwhelmingly positive. For example, if one of the "biggest" negative comments I heard was that we forgot to provide a return basket for the poster voting forms, then I am confident in saying we had a very good Symposium!

As in previous years, the Organizing Committee tried to improve the Symposium and the Technical Program, in particular. Of the many changes implemented, there are three I would like to mention here, and I ask for your feedback (e-mail me at Martin\_Keim@Mentor.com). The first change was the new program element of invited talks. Eight presenters were selected by the Session Chairs in cooperation with the Technical Program Chair for the purpose of kicking off a selected session and providing a framework, food for thought, an outlook, or similar context. How did you like these invited talks? Did they add value?

27

General Chair Martin Keim and the ISTFA 2016 Organizing Committee

The second change was increasing the number of paper presentations by adding a third parallel track on Monday afternoon. To be honest, we did not plan for this but were overwhelmed by the huge influx of high-quality paper submissions. Thank you! Many more papers made the cut of the predefined threshold of acceptance. We had the option of either cutting very good contributions and keeping the traditional two-track outline, or accepting papers based on their merits and expanding the program by adding a third track. We chose the latter.

The third change was a more thorough incorporation of the ISTFA theme. This year our theme was "The Next Generation," and it was featured in the excellent keynote

Local Student Poster Session participants from the University of Texas at Arlington with their advisor, Prof. Dereje Agonafer, and Dr. Felix Beaudoin, ISTFA 2016 Attendee Chair

presentation, "How to Educate the Next Generation IC Debug/FA Engineer at Academia," by Prof. Christian Boit and Dr. Philipp Scholz from the Technische Universität Berlin. Not only did the keynote speech show that it is quite possible for academia to educate students who are (continued on page 30)

#### **ISTFA SPONSORS**

On behalf of the Electronic Device Failure Analysis Society (EDFAS) and the organizers of ISTFA 2016, we appreciate your generous sponsorship contribution and recognize your continued commitment in making the ISTFA Conference and Exposition an outstanding event!

#### Sponsors Allied High Tech Products, Inc. BSET EQ Checkpoint Technologies, LLC FEI Company Mentor Graphics Nisene Technology Group, Inc. Quartz Imaging Corp. ULTRA TEC Manufacturing, Inc. Varioscale, Inc. Media Sponsors EDFA eNews EDFA Magazine

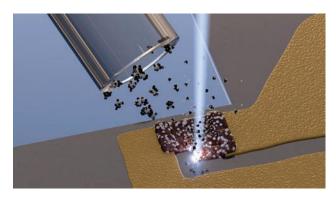

#### **Small Device Preparation**

• Open areas as small as 100 x 100 μm

#### **Complex Device & Stacked Die Deprocessing**

TSV exposure

Targeted stacked die exposure

#### **HD** Camera System

HD camera system with refined tool motion enhances ability to prepare sub millimeter area devices

Advancing Technology Through Sample Prep

The **X-Prep**<sup>®</sup> is a specialized 5-axis CNC-based milling/grinding/polishing machine designed to support electrical and physical failure analysis techniques and other applications through high precision sample preparation. This easyto-use, highly versatile system is capable of working with flat (2D) and convex/ concave (3D) device profiles, providing unmatched precision and accuracy.

- PREP \*

800.675.1118 US/Canada 310.635.2466 Worldwide info@alliedhightech.com www.alliedhightech.com 30

#### **ISTFA 2016–WOW!** (continued from page 27)

ready for their FA job, but it also provided a recipe for other universities on how to set up such a program. Next, the theme was at the center of the Panel Discussion, which quickly turned into a very interactive discussion among the audience and panelists. It was a pleasure to observe the passion, drive, and engagement of every participant. You will find a summary of the Panel Discussion on page 33 in this issue. Finally, the Student Poster Session featured ten contributions from two local universities: the University of Texas at Arlington with nine posters, and Rice University with one poster. I observed great interactions between the presenting students and the attendees, who were interested to learn about the students' research, which, by the way, is outstanding.

Other constants of the program returned to ISTFA 2016: two short courses were held on the Saturday before ISTFA; twenty tutorials were offered, including two new ones; four User Groups were held; and a sold-out Tools of the Trade Tour featured eleven companies.

#### DONE BY VOLUNTEERS

Of course, creating such a program involves hard work by many people, nearly all of whom are volunteers. These volunteers spend tremendous hours of their free time in various roles, all toward the goal of creating an outstanding Symposium. I cannot thank them enough for their hard work, but I can recognize them here: Vice General Chair Sam Subramanian (NXP Semiconductors), Past General Chair James Demarest (IBM), Technical Program Chair Efrat Moyal (LatticeGear), Attendee Chair Felix Beaudoin (Globalfoundries), Audio/Visual Chairs David Grosjean (Butterfly Network) and Zhigang Song (Globalfoundries), Expo Chair Becki Watt (Mentor Graphics), Tutorial and Short Course Chairs Susan Li (Cypress Semiconductor) and Mayue Xie (Intel), Panel Chairs Frank Altmann (Fraunhofer CAM) and Kendall Scott Wills (KAB Global Enterprises), User Groups Chairs Rick Livengood (Intel) and Baohua

Niu (TSMC), Local Arrangements Chair Becky Holdford (retired), and the Video Contest Chair Rose Ring (Qorvo). In addition to these Organizing Committee Chairs, there were 38 Tutorial and Paper Session Chairs as well as approximately 100 reviewers—all volunteers. The Organizing Committee was professionally supported by Kathy Murray, Lindy Good, and Christina Sandoval of ASM International and sponsored by EDFAS through its presidents Cheryl Hartfield and Zhiyong Wang.

The ISTFA Organizing Committee is always looking for new volunteers. If you would like to participate in organizing ISTFA or become a reviewer, please contact one of the ISTFA 2017 Organizing Committee members. You will find their contact information on the ISTFA 2017 webpage at istfa.org. If you have a suggestion for new tutorials or would like to create one, please go to the ISTFA 2017 webpage and submit your ideas.

#### **NOT ALL WORK**

ISTFA's Technical Program is taxing—a full program from early morning to early evening—so relaxing and mingling at the Social Event is a welcome break. This year's Social Event was held at Billy Bob's Texas, where we enjoyed good Texas BBQ, drinks, live music, and more. The highlight was a bull-riding event, where professional cowboys tried to stay atop a violently bucking bull for eight seconds. Great fun! Oh yes, someone must have told the band that the General Chair likes line dancing.

#### **COME BACK FOR ISTFA 2017**

In closing, ISTFA 2016 was a great success: an excellent Technical Program, a larger number of high-quality papers, and a growing number of attendees as well as companies displaying on the Expo floor. I invite you to come back for ISTFA 2017, which will be held November 5 to 9 in Pasadena, California.

## **EDFAS MEMBERSHIP**

Whether networking at events or accessing information through *EDFA*, ISTFA proceedings, or journals, our members have the edge. Now it's time to introduce EDFAS to others in the industry who would like to take advantage of these careerenhancing benefits. Help us help the industry by expanding our membership and offering others the same exceptional access to information and networking that sets EDFAS apart. To reacquaint yourself with and introduce others to the EDFAS member benefits, visit asminternational.org/web/edfas/membership.

# **STEADOT ASTRONOMICS AND FAILURE ANALYSIS** NOVEMBER 5-9, 2017 | PASADENA, CALIFORNIA, USA

#### Original, unpublished abstracts are being solicited in the following topic areas:

HALLEUR PAPE

- Emerging FA Techniques and Concepts

- Future Challenges of FA

- Fault Isolation (Thermal, Lock-in thermography, static and dynamic laser stimulation, static and dynamic emission microscopy, Laser Voltage Probing and imaging ...)

- 3D devices Failure Analysis (stacked dies, TSV ...)

- FA Techniques Addressing the Challenges of Heterogeneous Systems in Package

- Organic Electronic (OLED...)

- Wireless, Self-Powered, Sensors, MEMS Failure Analysis

- Detecting Counterfeit Microelectronics

- Alternative Energy (Photovoltaics, Solid State Lighting, etc...)

- Packaging and Assembly Level FA

- Diagnostic Testing, Scanning and Debug

- Board and System Level FA

- Metrology and In-line Device Characterization

- Power, Discretes and Optoelectronic Device FA

- Electronic Device Materials Characterization (SIMS, RBS, XPS, Auger, etc...)

- Microscopy (SEM, TEM, FIB, etc.)

- Circuit Edit (Laser, FIB, etc.)

- Sample Preparation and Device Deprocessing

- Scanning Probe Analysis

- Yield and Reliability Enhancement

- Nanoprobing, Electrical Characterization

- Competitive Analysis and Reverse Engineering

• FA Process

#### Abstract submission Deadline: April 21, 2017

Electronic Device Failure Analysis Society

Organized by:

#### Congratulations to the following winners:

#### ISTFA 2016 BEST PAPER:

"VLP... Demonstrating 110 nm Resolution in Common Laser Probing Applications"

Travis Eiles, Intel Corp.

#### **ISTFA 2016 OUTSTANDING PAPER:**

"Root Cause Analysis for Pin Leakage"

Zhigang Song, Globalfoundries

#### ISTFA 2016 BEST POSTER:

"Validation of DLS Data by LVP in Case of Marginal Failure"

Keonil Kim, Samsung Electronics System LSI Division

#### ISTFA 2016 STUDENT POSTER:

"Solder Ball Reliability Assessment of WLCSP through Power Cycling"

Bhavna Conjeevaram, University of Texas at Arlington

#### EDFAS 2016 PHOTO CONTEST WINNERS

#### Congratulations to the following winners:

#### **Category I: Color Images**

- 1st Jordan Hendricks, Hi-Rel Laboratories

- 2nd Eric Cattey, NXP Semiconductors

- 3rd Richard Park, Raytheon

#### **Category II: Black & White Images**

- 1st Nathan Wang, Maxim Integrated

- 2nd Lori Sarnecki, Fairchild Semiconductor

- 3rd Philipp Scholz and Heiko Lohrke, Technische Universität Berlin

#### **Category III: False Color Images**

1st Wentao Qin, ON Semiconductor

- 2nd Luigi L. Aranda, Raytheon

- 3rd Andrew Ozaeta, Raytheon

All winners received a recognition plaque or certificate and a one-year EDFAS membership. The winning entries will be featured on the cover of this magazine during 2017. They also may be viewed on the EDFAS website.

#### **EDFAS 2016 VIDEO CONTEST WINNER**

#### Congratulations to the following winner:

"ACETONEMENT aka: Where Did the Bond Wires Go?" by Timothy Hazeldine, ULTRA TEC

The winner received a complimentary registration to a future ISTFA conference and a first-place winner plaque. The winning entry may be viewed on the ISTFA 2017 website.

#### Advertise in Electronic Device Failure Analysis magazine!

For information about advertising in *Electronic Device Failure Analysis*, contact Erik Klingerman, National Account Manager; tel: 440.840.9826; e-mail: Erik.Klingerman@asminternational.org. Current rate card may be viewed online at asminternational.org/mediakit.

Frank Altmann Fraunhofer IMWS, Halle, Germany frank.altmann@fraunhofer.imws.de

failure analysis (FA) engineer's core business is to investigate and solve reliability problems of technologies for electronic applications by identifying process variations and root causes of defects and by suggesting corrective actions. An FA engineer must handle multiple FA techniques for defect localization, preparation, and physical analysis with continuously increasing complexity. In parallel, he needs sophisticated skills in communication because he often acts as an intermediary between different parties (fab, design, test, customer, etc.). Under these aspects, the ISTFA 2016 Panel Discussion was dedicated to the following topics:

- How is a typical FA lab organized? Which skills and levels of education are required for a future FA engineer?

- How does one go from being a specialist in a certain preparation or analysis method to being an experienced FA engineer ready for customer meetings?

- Which internal/external training programs are available (face-to-face or online)?

- Where does the money and time come from that is spent to become trained in FA?

The panel members were Professor Christian Boit, Technische Universität Berlin; James Cargo, Broadcom Ltd.; and Nebojša Janković, NXP Semiconductors. Each panel member has a long history of experience in FA work, education, training, and lab management.

The Panel Discussion was introduced by Nebojša Janković. He pointed out that a typical FA lab is organized by FA engineers as job owners being responsible for performing hands-on electrical FA and physical characterization, with the emphasis on software- and hardware-based device fault localization. Only highly specialized investigations are done by dedicated engineers. Standardized physical analysis steps are mostly done by a technician crew. Strong preference should be given to mixed-signal IC design, test, and layout understanding.

## "AN FA ENGINEER SHOULD BE EDUCATED TO THE ACADEMIC LEVEL OF A MASTER'S OR Ph.D. DEGREE IN TECHNICAL SCIENCES AND THEN MUST SEEK CONTINUOUS LEARNING AND TRAINING."

Furthermore, an FA engineer should have experience with memory devices, especially nonvolatile options, as well as reverse engineering skills, including IC process technology knowledge. Responsibilities should include not only the use of existing and available equipment, techniques, and methods but also the development of new methods and techniques. An FA engineer should be able to work independently but also to cooperate with peer product, test, design, and process engineers as well as customers. In addition to technical skills, he must also be a good team player. An FA engineer should be educated to the academic level of a Master's or Ph.D. degree in technical sciences and then must seek continuous learning and training. With the experience and routine from internal customer meetings, he also strengthens the communication skills necessary to take care of end-customers' needs. This can be managed by additional coaching and mentoring on the job, focused on having an outside view and an endcustomer's perspective. A typical beginner learns the first skills and tools internally on the job, being mentored and trained by an experienced FA engineer. External courses must follow for certain specialized methods and tools.

After the introduction, an intense open discussion began between the panelists and the audience. It was discussed that FA spans a large breadth of topics and educational disciplines, and almost no undergraduate programs are available at universities. Linking to the keynote presentation, "How to Educate the Next Generation IC Debug/FA Engineer at Academia," Christian Boit mentioned that the educational concept begins with standard lectures on electronic circuitry, IC design, and semiconductor devices, followed by design verification and debug/FA. This educational concept is mature, proven, and ready to be integrated into electrical engineering curricula worldwide. Furthermore, he pointed out that an FA engineer has an exciting job and is in good hands within a great FA community. He said, "Being an FA engineer is like entering 'Hotel California': You can check in but cannot check out," meaning that one stays in touch with this topic over the long term, because the knowledge to make a quality FA engineer grows over many years.