AUGUST 2016 | VOLUME 18 | ISSUE 3

# **ELECTRONIC DEVICE** FAILURE ANALYSIS

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

edfas.org

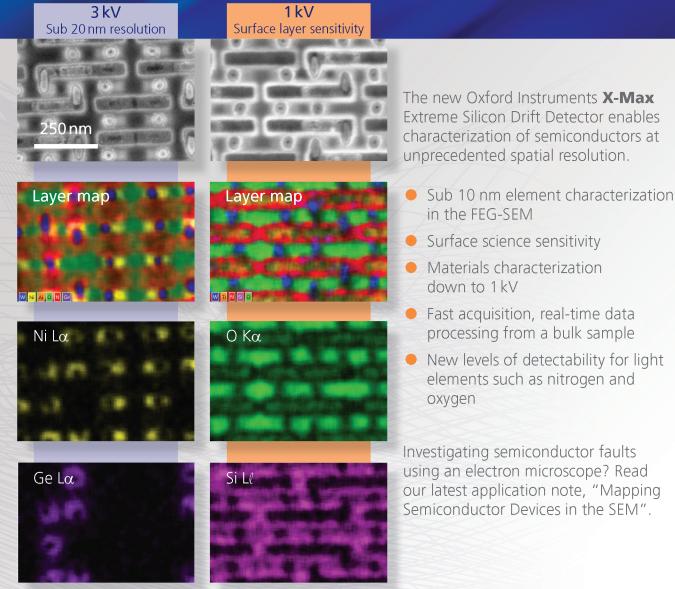

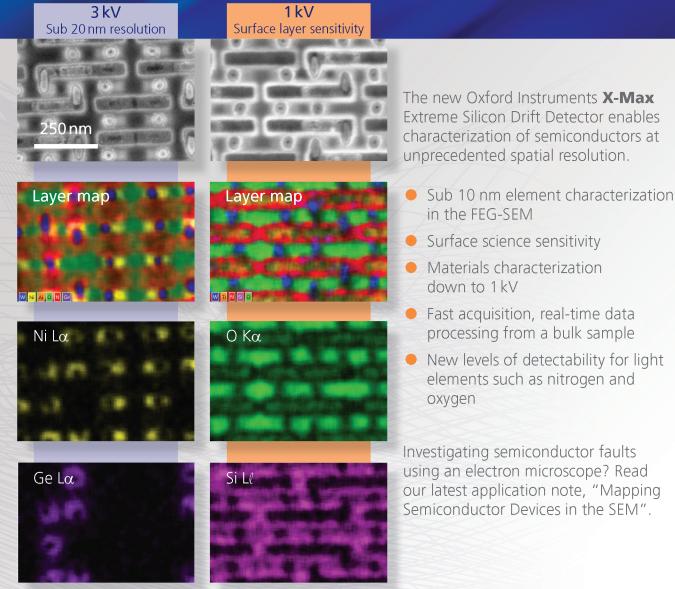

# EXTREME EDS

# X-Max<sup>®</sup> Extreme SDD

# A gamechanger in materials characterization in the SEM

With just two 6 minute maps it is possible to fully characterize a bulk semiconductor device. At 3 kV all elements in the specimen can be resolved to sub 20 nm resolution. At 1 kV light elements can be mapped with high surface sensitivity and 10 nm lateral resolution.

For more info and to download our free application notes: **www.oxinst.com/extreme**

The Business of Science®

AUGUST 2016 | VOLUME 18 | ISSUE 3

# ELECTRONIC DEVICE FAILURE ANALYSIS

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

# ISTFA 2016 PREVIEW PAGE 32

4

10

HIGH-VOLTAGE CAPACITOR FAILURE ON A DOWNHOLE OILFIELD PCB

MANAGEABILITY CHALLENGES FOR INTERNET OF THINGS

edfas.org

TAKE A CLOSER LOOK AT ELECTRICALLY-Enhanced Lada: Setup

**ESREF 2015 IN TOULOUSE**

# ASAP-1<sup>®</sup> IPS Interactive Preparation System

- Realtime Video Monitor with System Parameters Always Live

- Huge Cavity Size Range <0.25mm<sup>2</sup> to >1,600mm<sup>2</sup>

- Endpoint option suits package pre-cavitation

- X, Y and Z Axes all have industry leading deep sub-micron accuracy

- **Open System Design** allows for fixturing all types and size of part from surface-mount components, up to Motherboards, and 200/300mm Wafers

- Touch-screen control with physical Joystick and Controls Best of Both Worlds

- Unique Thermal Relaxation, Curvature Compensation, and Parametric (PEEC) options expand application range

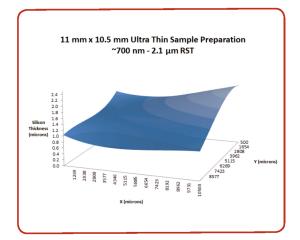

- Meet Current SIL Requirements (demonstrated 50µm RST +/- 2µm on Flip Chip), and Single Digit RST.

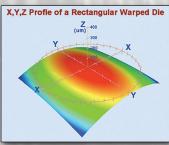

### MEET 3D & CURVED/WARPED SURFACE CHALLENGES WITH ADVANCED TECHNIQUES

#### **Curvature Compensation**

- Auto-Curve and Auto-tilt Setup

- Independent X & Y Axes

- Convex & Concave Surfaces

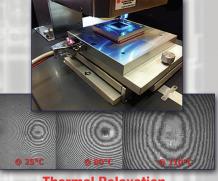

### Thermal Relaxation Safe and Reliable method to turn complex

- 3D scenarios into simpler 2D ones

- Reduces dynamic flex of substrate during preparation

- In-situ Hotplate Mode for sample mounting

#### FILMETRICS F3 Wafer Thickness Measurement System

- Multiple or single-point measurements

- Both 2D and 3D data generated

- Provides Information for achieving final uniformity

ULTRA TEC

All Package Types & Sizes • Parts can be decapped, thinned & polished in as little as 45 minutes

Toll Free (US) 1-877-542-0609 Tel: 1-714-542-0608 Fax: 1-714-542-0627 e-mail: info@ultratecusa.com www.ultratecusa.com

# ELECTRONIC DEVICE

edfas.org

# 4 High-Voltage Capacitor Failure on a Downhole Oilfield PCB

#### John Bescup

Passive components remain an integral part of today's circuit design. Read about the unlikely failure mode of a high-voltage leaded-ceramic-chip capacitor for downhole application.

# 10 Take a Closer Look at Electrically-Enhanced LADA: Setup

S.H. Goh, B.L. Yeoh, G.F. You, Y.H. Chan, Zhao Lin, Jeffrey Lam, and C.M. Chua

This article details the fundamentals behind EeLADA, a technology evolution in extracting relevant signals for debugging soft and hard failures.

### 18 Manageability Challenges for Internet of Things

#### Yen-Kuang Chen

The Internet of Things concept is the "next big thing," but what are the obstacles to achieving that vision? Device failure, sensitivity, scalability, middleware, and user interaction are challenges for this evolving technology.

# 22 ESREF 2015 in Toulouse

#### Marise Bafleur and Philippe Perdu

This review includes highlights from the 26th ESREF symposium, which focused on aeronautic, space, and embedded systems in 2015.

### **DEPARTMENTS**

- 32 SPECIAL! ISTFA 2016 AND EXHIBITORS LIST Martin Keim

- **30 2016 PHOTO CONTEST**

- 31 2016 VIDEO CONTEST

- **56 ADVERTISERS' INDEX**

- 36 BOARD OF DIRECTORS NEWS Bill Vanderlinde

- 52 DIRECTORY OF FA PROVIDERS Rose Ring

- 54 GUEST COLUMNIST Lihong Cao

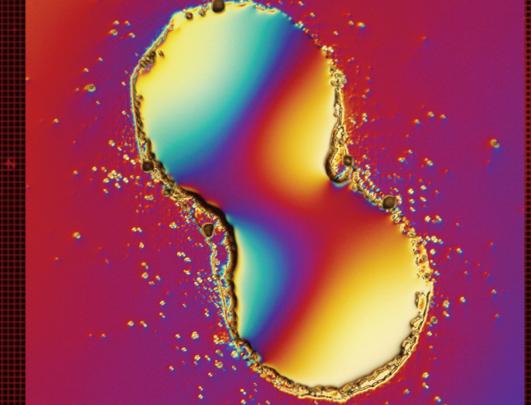

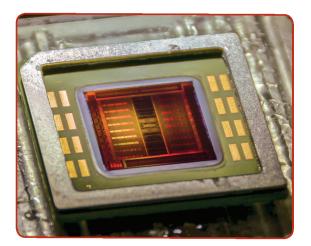

# **ABOUT THE COVER**

In situ solid immersion fabrication lenses created by randomly scattering polyethylene spheres across the backside of a die, then melting the spheres to form microscopic etch masks. The sample was plasma etched, and the plastic was removed. The sample was polished using colloidal silica. The lens shapes formed naturally due to the dynamics of polishing. The photo was taken using differential interference contrast. *Photo by Mark Kimball, Maxim Integrated Circuits. First Place Winner in False Color Images, 2015 EDFAS Photo Contest.*

### **Author Guidelines**

Author guidelines and a sample article are available at edfas. org. Potential authors should consult the guidelines for useful information prior to manuscript preparation.

2 GUEST EDITORIAL

Nebojša Janković and Frank Zachariasse

- 48 INVENTOR'S CORNER R. Aaron Falk

- 50 LITERATURE REVIEW Mike Bruce

- 40 PRODUCT NEWS Larry Wagner

- 46 TRAINING CALENDAR Rose Ring

For the digital edition, log in to edfas.org, click on the "News/Magazines" tab, and select "EDFA Magazine."

A RESOURCE FOR TECHNICAL INFORMATION AND INDUSTRY DEVELOPMENTS

#### AUGUST 2016 | VOLUME 18 | ISSUE 3

PURPOSE: To provide a technical condensation of information of interest to electronic device failure analysis technicians, engineers, and managers.

**Felix Beaudoin** Editor/Globalfoundries; felix.beaudoin@ globalfoundries.com

Scott D. Henry Publisher

**Mary Anne Fleming** Manager, Technical Journals Annie Beck **Production Supervisor Liz Marguard**

**Managing Editor**

#### OCIATE EDITORS

Michael R. Bruce Consultant David L. Burgess **Accelerated Analysis**

Lihong Cao Consultant

**Jiann Min Chin** Advanced Micro Devices Singapore

Edward I. Cole, Jr. Sandia National Labs James J. Demarest

IBM **Christopher L. Henderson** Semitracks Inc.

**Jason M. Higgins** TSMC (Wafertech) **Bobby Hooghan** Weatherford Laboratories

**Eckhard Langer** Globalfoundries

Philippe H.G. Perdu **CNES** France

Rose M. Ring Globalfoundries

H.S. Silvus, Jr. Southwest Research Institute

E. Jan Vardaman TechSearch International, Inc.

Martin Versen University of Applied Sciences Rosenheim, Germany Lawrence C. Wagner

LWSN Consulting Inc.

#### GRAPHIC DFSIGN www.designbyj.com

#### FSS RELEASE SUBMISSIONS

magazines@asminternational.org Electronic Device Failure Analysis™ (ISSN 1537-0755) is pub-lished quarterly by ASM International', 9639 Kinsman Road, Materials Park, OH 44073; tel: 800.336.5152; website: edfas. org. Copyright© 2016 by ASM International. Receive *Electronic* Device Failure Analysis as part of your EDFAS membership of \$88 U.S. per year. Non-member subscription rate is \$135 U.S. per year

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by ASM International for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$19 per article is paid directly to CCC, 222 Rosewood Drive, Danvers, MA 01923, USA. *Electronic Device Failure Analysis* is indexed or abstracted by Compendex, EBSCO, Gale, and ProQuest.

# **GUEST EDITORIAL**

# WHO IS A FAILURE ANALYSIS ENGINEER?

Nebojša Janković and Frank Zachariasse. NXP Semiconductors

nebojsa.jankovic@nxp.com frank.zachariasse@nxp.com

# **MISSION STATEMENT OF FA**

Failure analysis (FA) is an activity that serves to improve business and minimize losses for a company and its customers. The core business of FA is to solve problems for our customers by identifying both the root cause of errors made in production or design and by suggesting actions to rectify that cause. All our other activities (developing new methods, buying/maintaining equipment, refining skills) are pursued solely as a means to further the core business goal of solving our customers' problems.

### PHILOSOPHY OF FA

#### Failure analysts should strive to be masters of their craft. This means they should be skilled in applying multiple FA techniques and/or FA tools.

Failure analysis is a craft. The failure analyst applies his/her understanding of the IC together with skill in applying various FA techniques, which may imply using multiple FA tools, to bring the investigation to a successful conclusion.

The key ingredient in successful FA, apart from a solid theoretical background and a logical, inquisitive nature, is for the failure analyst to have access to a "toolbox" of techniques. The results of each of these assets can shed a new and different light on the problem. It is by combining the outcomes of these FA techniques, together with what is already known about the problem, that subsequent steps are guided toward the solution. Therefore, it is a requirement that a failure analyst, when fully trained, should be the master of a range of skills and tools and should be able to apply them judiciously to reach the end goal: solving the customer's problem.

#### Each technique shall be mastered by multiple failure analysts in the group. An analysis is conducted, as far as is practicable, by one analyst applying various techniques, rather than passing the problem from one "limited-scope" expert to another.

This second aspect to the philosophy means that multiple engineers and technicians must be trained in each technique. That is, for a well-run FA lab, there is no technique that only one person can perform. This applies to the major fault-localization and sample-deprocessing techniques.

This goal has three important beneficial effects:

• It results in the ability to discuss the approach and results with peers who are fully versed in the technique and who may suggest alternative

#### edfas.org

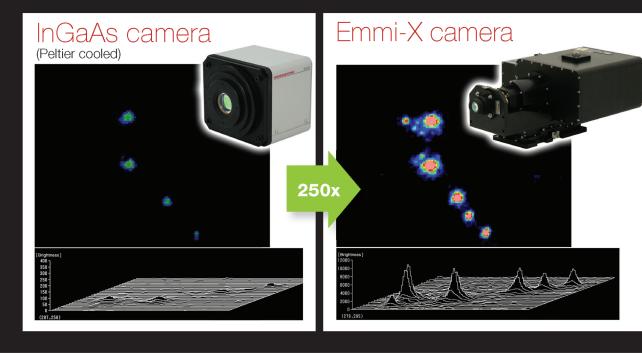

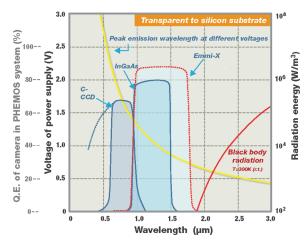

# Struggling to see photoemissions at low voltages?

The mobile market demands lower power consumption and Hamamatsu's **Emmi-X** camera delivers unprecedented sensitivity for the low voltage devices of the future. With **250X higher sensitivity** than typical TE cooled InGaAs cameras, the **Emmi-X** will ensure photoemission is your go-to technique for years to come.

Lower Vdd means fainter emissions and at longer wavelengths — requiring extended sensitivity.

Available for these systems: PHEMOS | iPHEMOS | THEMOS | TriPHEMOS

# Learn more at www.hamamatsu.com or call 858-210-6703

# HIGH-VOLTAGE CAPACITOR FAILURE ON A DOWNHOLE OILFIELD PCB

John Bescup, Weatherford John.Bescup@Weatherford.com

# **INTRODUCTION**

Often in technical discussions within the failure analysis community, passive components are overlooked in favor of novel analysis methods or emergent challenges to semiconductor reliability. However, passive components still occupy a vast amount of real estate in today's circuit designs and are not poised to disappear anytime soon. With that in mind, this article presents a case study of a failed high-voltage leaded-ceramic-chip capacitor that met its demise through an unlikely failure mode, which highlights the importance of well-trained operators behind the inspection equipment deployed to prevent latent defects.

# **DOWNHOLE APPLICATION**

The capacitor to be examined in this article was intended for use in the high-vibration and high-temperature realm of oil drilling, which has a set of reliability concerns familiar to automotive and aerospace engineers. The components on these printed circuit boards (PCBs) will ride behind the drill bit, penetrating deep into the harsh environment of the Earth's crust, where they will help perform measurements to evaluate the rock formations around them. That information is communicated in real-time to engineers on the surface who are guiding the drilling string toward its intended target. Because of the abusive operating conditions and the harsh penalties for electronics failures, all components must be thoroughly vetted and their failure modes understood.

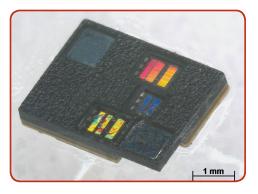

During the qualification of a new board design, a high-voltage ceramic-chip capacitor had failed by shorting itself. This part is rated for high temperature and has leads soldered onto its terminations with a high-meltingpoint solder. In many circuit designs, a single shorted capacitor may not influence the overall functionality and may escape completely undetected; however, this particular component played a vital role, directly impacting board functionality. Surprisingly, this part had already "OFTEN IN TECHNICAL DISCUSSIONS WITHIN THE FAILURE ANALYSIS COMMUNITY, PASSIVE COMPONENTS ARE OVERLOOKED IN FAVOR OF NOVEL ANALYSIS METHODS OR EMERGENT CHALLENGES TO SEMICONDUCTOR RELIABILITY. "

undergone qualification studies on a different PCB with similar operating conditions and had been in use for some time. So, why had this particular unit failed?

# **EXTERNAL ANALYSIS**

During electrical troubleshooting, a technician had identified a suspect appearance on the terminations of this capacitor. When the component was replaced with a brand new part, board functionality was restored and testing continued without incident. The failed component was given an initial optical inspection, which revealed two points of interest:

- Metal migration from the termination onto the capacitor face was observed from both sides of the part.

- The high-melting-point solder, which held the leads in place, had clearly reflowed and was showing heat-stress discoloration.

Both of these conditions can be seen in the optical images in Fig. 1.

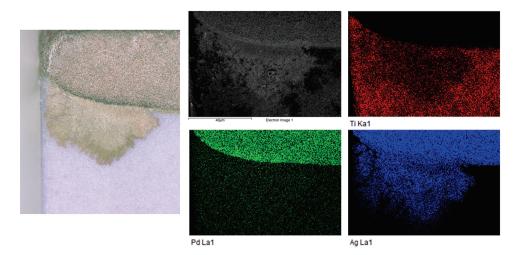

Metal migration via dendritic growth mechanisms is a threat particularly where high-voltage conditions exist, such as for this 2000 V capacitor. However, an examination of all sides of the capacitor quickly determined that the dendrite growth had not progressed far enough to create an external bridge between the terminations. To determine the nature of the dendritic growth, energydispersive spectroscopy (EDS) was performed. By creating the series of element maps shown in Fig. 2, it was determined that silver had migrated onto the capacitor face. The other principal component of the termination material, palladium, had remained completely in place. As foreshadowing, note that the internal capacitor plates also contain silver.

While the capacitor was in the scanning electron microscope (SEM) chamber, elemental quantification data were also gathered on the solder to verify that it had the intended composition. Because components in the oil-drilling industry are pushed into very extreme operating environments, a restriction of hazardous substances exception allows these boards to use leaded solder. A rectangular-area EDS spectrum acquired over the discolored area where the lead joins the cap termination showed 75/23 lead/tin, with the balance being silver. This is a close-enough match to the expected composition to rule out the possibility that the solder joint had been contaminated with a low-temperature solder during manufacture. Because component and PCB manufacturers who provide high-temperature assembly always offer low-temperature products as well, the possibility of inadvertently mixed solder alloys is a constant threat to reliability that must be guarded against. Consulting the tin-lead phase diagram, the liquidous point of 75% lead solder is just above 500 °F, so our termination certainly experienced some heat in order to discolor and partially reflow.

### NONDESTRUCTIVE INTERNAL ANALYSIS

Before going further, it is necessary to understand a bit more about the construction of this particular component.

(a)

#### (b)

Fig. 1 (a) Optical image showing overall view of the failed capacitor. Note dendrite growth at upper right and the reflowed termination solder with heat-stress discoloration on the right side. (b) Closeup of dendritic growth from termination onto the cap face

Fig. 2 EDS mapping of the dendrite growth. Starting at top-middle image and going clockwise: SEM grayscale image, red titanium map, blue silver map, green palladium map, and color optical image

#### edfas.org

Most capacitors use two sets of plates, with one connected directly to each termination. For high-voltage parts such as this one, manufacturers often add a third set of "floating" plates in the center of the part that are not directly connected to anything. This effectively creates two capacitors in series. The advantage of this arrangement is a little extra assurance that if a void or a particle of debris were present inside the capacitor dielectric, causing a short between the termination plates and the floating plates, there would still be another set of plates preventing the part from being completely shorted. Furthermore, to create a short on a capacitor built this way, it would be necessary for the left set of termination plates to bridge with the floating plates in the center and the right-hand set of termination plates to also be shorted with that *exact* same floating plate. Statistically speaking, the likelihood of this scenario is low. For this reason, the contention that this capacitor was shorted internally because of voiding-related plate bridging was viewed with strong skepticism.

Acoustic microscopy is often used by capacitor manufacturers to screen out parts that have been compromised by voids or debris in the dielectric material between plates. Although air is technically an insulator, voids in the capacitor dielectric can facilitate several failure modes that otherwise would not be possible. Migration of the plate metal can occur, as already seen on the outer surface, and humidity can condense under the high-temperature conditions in which this part will be operating. Most of the time, ultrasonic inspection is relatively straightforward and forgiving in the sense that even when parameters are not perfectly optimized, it is still possible to spot any notable defects. Among the many imaging modes available on a modern acoustic microscope, two time-tested methods will find nearly any defect in a typical capacitor: bulk scan and loss-of-back-echo (LOBE) scan. Because high frequencies of ultrasound cannot propagate through

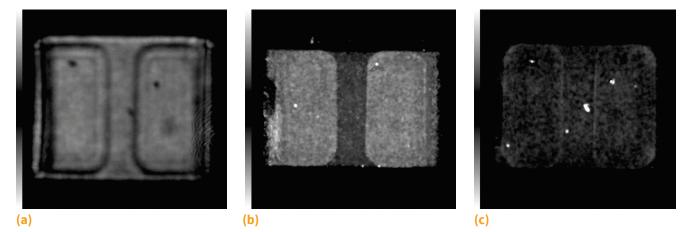

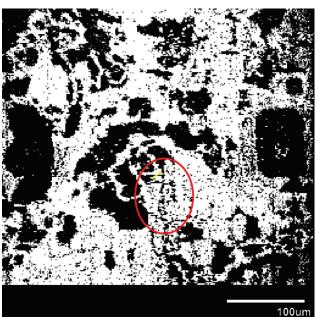

air, even incredibly small pockets of air are very effective at reflecting an ultrasonic signal sent into the capacitor. The LOBE technique uses this concept to advantage by depicting the shadows where the ultrasonic signal was blocked when the microscope captures a backside image of the part. In this way, features such as diagonal cracks, which scatter the sound without returning it to the transducer, can still be spotted. So, the name of the imaging mode describes exactly how it works: Any echo that is lost by the time it reaches the back surface of the part tells the operator something. The LOBE scan in Fig. 3(a) shows a few dark areas, which can be checked against forthcoming scans.

The other main inspection method used to search for defects in cap dielectric is bulk scan, where the image is generated by only those reflections originating from inside the part, purposely excluding the front and back surface reflections. In this imaging mode, bright reflections represent air gaps inside the bulk of the dielectric. Figures 3(b) and (c) show two bulk scans of the shorted capacitor. When creating these images, the transducer is typically focused halfway between the front and back surface, which, in this case, was measured to occur at a time of flight (TOF) equal to 13.9 µs. However, when this accepted convention is used, the resultant image shows no voids at the locations indicated by the LOBE scan. After repeating the scan with a higher and lower TOF, the operator discovered that different sets of voids were revealed, depending on the transducer focus. The particular combination of materials used in this dielectric material is restricting the acoustic depth of field. This is not normally the case, and it gives a plausible reason why acoustic inspection at the time of manufacture may have missed a set of voids that did not appear when the acoustic microscope was configured according to customary settings for bulk scan inspection. The image in Fig. 3(c), which was created with a TOF equal to 10.2 µs, reveals

Fig. 3 (a) LOBE acoustic image. (b) Bulk scan acoustic image with TOF at 13.9 μs. (c) Bulk scan acoustic image with TOF at 10.2 μs

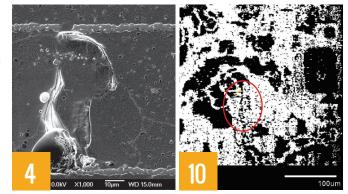

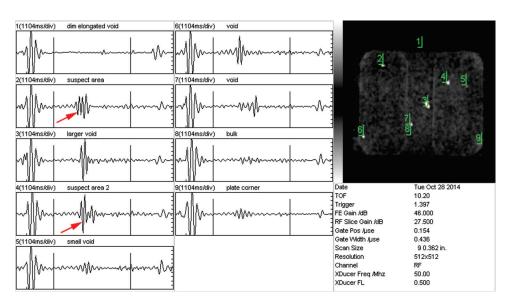

Fig. 4 Acoustic waveform capture displaying many points of interest. Red arrows highlight echoes from two voids at a nearly identical depth from opposite sides of the capacitor.

a set of voids where dark shadows in the corresponding LOBE image (Fig. 3a) had indicated. Two of these will be of particular interest moving forward.

As mentioned previously, to create a short between two terminations, there must be a short path from both terminations to the same center plate. To determine if this scenario were possible with the voids seen in acoustic imaging, a closer examination of the waveforms used to build these images is needed. The image in Fig. 4 shows a variety of waveforms sampled from the failed part. Red arrows on the waveform from positions 2 and 4 point out echoes from two voids at the same position in time, which also corresponds to depth in acoustics. These two voids also have an unusual appearance, with dark halos surrounding them, which increases interest in them. X-ray inspection was also performed on this capacitor, although as an inspection method it is better suited for finding large cracks beneath the terminations, where acoustic microscopy has difficulty seeing. In this case, nothing noteworthy was found via x-ray, so the decision was made to proceed with cross sectioning and finding out exactly what acoustic inspection had seen.

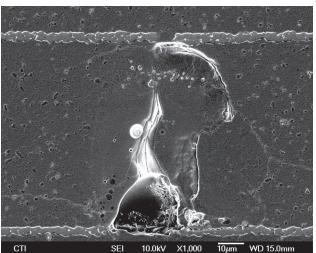

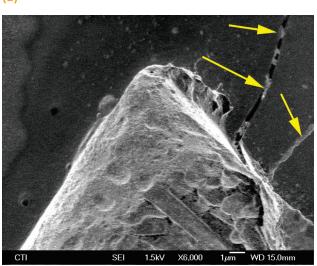

### CROSS SECTIONING AND SEM ANALYSIS

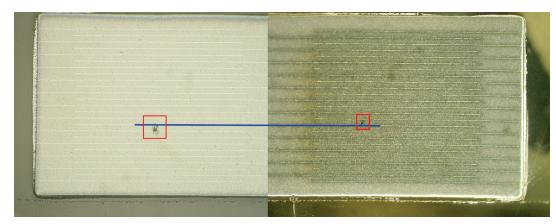

Using the acoustic images as a guide, the failed capacitor was cross sectioned to obtain a direct look at the two suspect voids and to verify which plates they contacted. A composite optical image shown in Fig. 5 depicts both voids, although they were not physically visible at the same time because of the direction of the cross sectioning. In this image, a blue line has been superimposed along the length of one of the floating plates to illustrate that, indeed, both of these voids make contact with the same floating plate.

Fig. 5 Composite optical image showing cross-sectioned views of the two voids previously identified by acoustic inspection. The voids are highlighted with red rectangles; a blue line traces the connection to the center floating plate that these voids share.

#### edfas.org

(a)

(b)

Fig. 6 (a) SEM closeup showing a void that stretches completely between a termination plate and a floating plate. (b) SEM closeup with yellow arrows highlighting metal migration within cracks that extend from the larger void cavity between plates

To inspect the voids at higher magnification, the SEM was used. A detailed view of the void from the left half of the optical view is shown in the SEM image in Fig. 6(a). In close-up images, it can be noted that the capacitor plate material has either melted or migrated into the air gap in the dielectric material. As previously noted, silver—a major component in the plates—can certainly migrate, as the EDS inspection showed. Both voids had a network of fine cracks extending from the air cavity, likely induced by expansion and contraction as the part was exposed to high

temperature during testing. Although these cracks are small in scale, the metal from the plate material is clearly seen filling in these cracks, as noted by the yellow arrows in Fig. 6(b). This metal ultimately created the electrical pathway that led to the capacitor failure.

### **SUMMARY**

After investigating the capacitor with a variety of methods, it was seen that internal shorting via silver migration was the failure mode. It is believed that this was a latent defect caused by voids in the dielectric that had been present from the time of manufacture. Through some combination of time, electric potential, trapped humidity, and elevated operating temperature, the plate material migrated into these voids and created a short path to the same floating plate. Acoustic imaging proved to be the best method for detecting the point where this failure had occurred, although it was also clear that, in this case, a single-pass inspection with the conventionally accepted parameters was not able to find the voids of interest.

#### **ACKNOWLEDGMENT**

The author would like to thank his colleagues Fardin Farzaneh, Chris Yarbrough, and Bobby Hooghan for all their assistance.

### **ABOUT THE AUTHOR**

John Bescup is an electrical engineer for Weatherford. He has more than 10 years of failure analysis experience, with an emphasis in acoustic imaging. His day-today routine includes diagnosing a variety of nonfunctional hardware, covering the gambit of failure analy-

sis disciplines from component-level reliability (package and semiconductor) to board/assembly-level vibration effects or corrosion on metal parts. John has served as an instructor for numerous acoustic imaging training sessions worldwide, been a tutorial session presenter at the International Symposium for Testing and Failure Analysis 2014-2015, and presented at the 2016 ASM Failure Analysis and Prevention Seminar, upon which this article is partially based. He received his B.S. in engineering physics from the University of Wisconsin, Platteville in 2005.

#### edfas.org

# WHEN FA = FASTANSWERS FOR FAILURE ANALYSIS

Look to JEOL for reliable imaging and analytical tools designed for both routine and exacting failure analysis.

JEOL SEMs, TEMs, and sample preparation instruments are versatile, easy to use, and an uncompromising choice when it comes to valuing your time, yield, and bottom line.

JEOL USA is #1 in service, technical and applications support.

#### Fast Answers with High Resolution Imaging and Analysis

- All-in-One Analytical Field Emission SEM

- Compact, High Throughput SEM

- Cross Section Polisher with Specimen Cooling/Air Isolation

- Atomic resolution Cs Corrected TEM with Cold FEG

- Large Angle SDD-EDS, Automated S/TEM

- Benchtop ED-XRF Elemental Analysis

SCANNING ELECTRON MICROSCOPES • TRANSMISSION ELECTRON MICROSCOPES • CORRELATIVE MICROSCOPY • SAMPLE PREPARATION TOOLS

salesinfo@jeol.com • 978-535-5900

For more information visit www.jeolusa.com/jeolFA

# **TAKE A CLOSER LOOK AT ELECTRICALLY-ENHANCED** LADA: SETUP

S.H. Goh, B.L. Yeoh, G.F. You, Y.H. Chan, Zhao Lin, and Jeffrey Lam Globalfoundries, Technology Development, Product/Test and Yield Engineering, Singapore

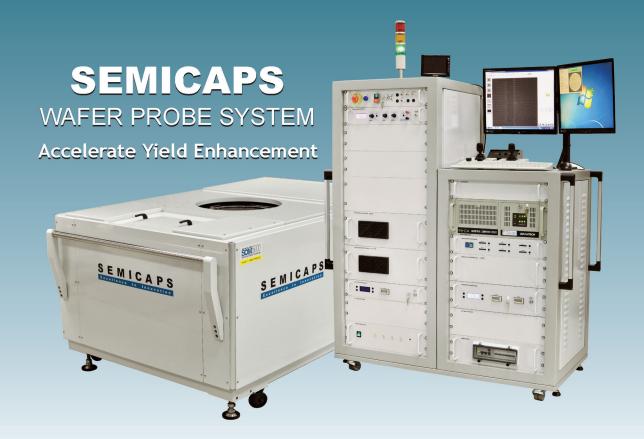

> and C.M. Chua, Semicaps Pte Ltd., Singapore SzuHuat.Goh@globalfoundries.com

# **INTRODUCTION**

On sub-28 nm process technology, silicon patterning conformance to design, especially front-end-of-line, has run up against the limits of physics, bringing about a paradigm shift from defect-limited hard failures to increasing occurrences of design-margin soft failures as a result of the shrinking process window. Therefore, the role of soft defect localization (SDL) techniques in yield engineering has become more important. It is common to speak of SDL and laser-assisted device alteration (LADA) when such failures need to be investigated.

LADA uses a continuous-wave 1064 nm photocurrent-inducing laser to temporarily alter transistor characteristics through the silicon substrate. The outcome is a flip in the tester pass-fail state. The position of the scanning laser is correlated to the state transition and registered for signal image acquisition.<sup>[1]</sup> Such an approach is well known to be effective for localization of speed path degradation<sup>[2]</sup> and subtle process defects.<sup>[3]</sup> The application of LADA extends beyond such spatial localization with the innovation of time-resolved LADA (TR-LADA), which is capable of extracting temporal information from the failures by using a 1064 nm pulsed laser to "probe" different test cycles in each test loop.<sup>[4]</sup> It offers new insights, such as failure mode identification<sup>[5]</sup> and knowledge of propagation delays.<sup>[6]</sup> In some cases, an improved LADA signal spatial resolution has also been observed.<sup>[7]</sup> The current state-of-the-art in TR-LADA is based on a 50 ps pulse-width laser that enables the interrogation on a single test cycle. As a matter of fact, both LADA and TR-LADA signals can be attributed to either potential sites of existing issues or devices with low threshold to laser stimulation, the latter also known as artifacts. There is no means to intuitively differentiate between the two by merely monitoring the transition of test pass-fail states. This is the main motivation behind the innovation of electrically-enhanced

LADA (EeLADA).<sup>[8,9]</sup> It works by the concept of eliminating these artifacts by extracting fail information from all LADA events in terms of failing pins/cycles and comparing them against the actual fail information derived from testing the bad unit.<sup>[7]</sup> In this way, only the LADA signals relevant to the actual failure will be displayed. This methodology also presents an advancement that overcomes LADA's traditional limitation on soft failures and creates new possibilities for hard failure defect localization. The concept of EeLADA can be realized in a number of ways, and two such approaches will be discussed.

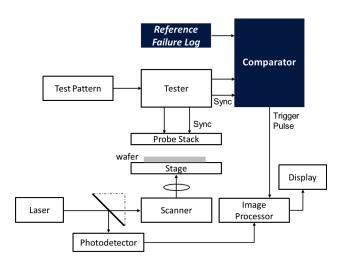

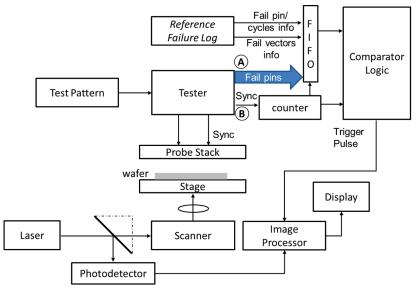

### WHAT IS ELECTRICALLY-ENHANCED LADA?

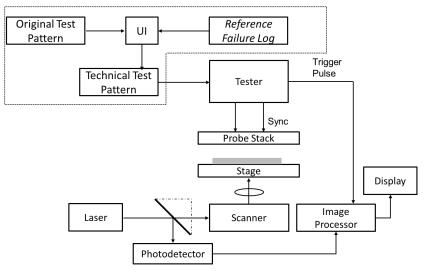

Figure 1 shows a block diagram illustrating the EeLADA concept. In general, although the setup refers to a waferlevel configuration, it applies to package level as well. Unlike a typical synchronous LADA setup where the tester generates a trigger in the event of a flip in the test state, EeLADA integrates an additional comparator module to determine the trigger pulse generation. The integrated circuit (IC) device under test is activated by the tester, which refers to the test pattern for the biasing conditions. A test pattern is defined by a three-dimensional matrix of test vectors that correspond to specific pin names and cycle numbers. The test vectors may represent inputs or outputs. Inputs serve as driving signals into the IC, and outputs, also called compare test vectors, provide the expected states to determine a test pass-fail.

Prior to debug on EeLADA, the bad IC is tested, and a standard failure log containing details of the compare fail vectors and the respective fail pin/cycles is obtained. This is referred to as the reference failure log, as shown in Fig. 1, and is called the reference failure signature. The comparator module receives this fail log and commits it to memory. As the tester activates the soft failing IC and the

Fig. 1 Block diagram of EeLADA concept

laser stimulates the region of interest, the test outcome is compared against the reference failing signature at each pixel. In the event of a match, a trigger pulse is generated by the comparator module and sent to the image processor. This is how LADA signals that are not directly relevant to the reference failing signature are negated on the display.

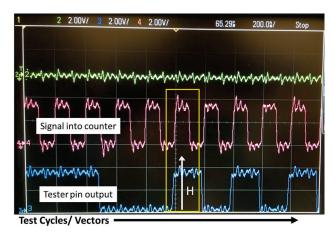

# HARDWARE APPROACH

Figure 2 shows a block diagram illustrating a hardware implementation of EeLADA. As apparent in the earlier section, the essence of the concept lies in the realization of the task of the comparator logic. A first-in-first-out (FIFO) buffer array of sufficient depth functions as the memory to capture the reference fail signature. Electrical channels on the prober interface board that relate to the failing pins (based on the reference fail signature) are wired out and passed into another set of FIFO buffer arrays to capture the pin output state at each test cycle. A pulse that is generated by the tester within each test period synchronizes a counter with the test cycle. The counter increments the shifting of the FIFO arrays and coordinates the comparator logic circuit to access the FIFO states at the failed cycles for matching. As an illustration, a passing IC is tested, and waveforms captured at the points labeled "A" (tester pin output) and "B" (signal into counter) are observed on an oscilloscope. An example based on a few test cycles is shown in Fig. 3. An instance of a test cycle is denoted by a bounding box, and the arrow indicates the expected compare vector (H). The output pin attains a voltage high, which is correct.

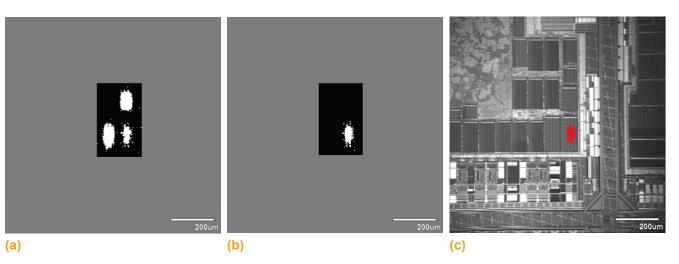

The results of another simple experiment accomplished on memory built-in self-test are presented in Fig. 4. The sample under test is a good IC. Figures 4(a) and (b) show the LADA and EeLADA signals, respectively, on three embedded memory arrays. With selective pin/cycle matching, only one of the memory arrays is revealed,

with the rest "electrically filtered." Figure 4(c) shows the overlay image. This result demonstrates the feasibility of the technology.

Additionally, it should be noted that the criteria for matching can be determined by the user. For example, a trigger pulse can also be generated as long as one of the current fail vectors matches to any of the failed vectors in the reference signature. In this case, more signals are expected to be observed in the image as compared to an exact match, because the comparison scheme is less stringent.

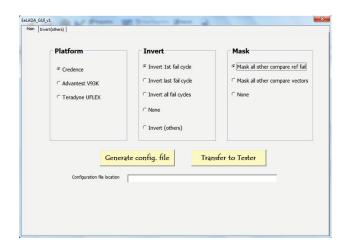

### SOFTWARE APPROACH

Another approach to realize EeLADA is illustrated by the block diagram in Fig. 5. Unlike the hardware approach, there is no comparator logic involved to assess a match situation. Instead, a graphical user interface (GUI) receives the original test vectors as well as details of the failing signature to generate a technical test pattern dedicated for defect localization. To explain the methodology, consider a simple case of a failure signature consisting of only a failed vector that corresponds to a certain fail cycle and pin. Assuming this specific compare vector is failing, a "High" is expected; that is, it attains a "Low" on the test. The original vectors that correspond to the failing signature are inverted. In this case, instead of expecting a "High," the test now expects a "Low" for this compare vector to pass. Therefore, the test will fail by default when the technical test pattern is employed. As the laser induces LADA signals that give rise to failing compare vectors other than the inverted vector, the test state remains unchanged. Conversely, when the LADA signal matches the failing signature, there is a state change to pass, and a match trigger signal is provided directly from the tester to the image processor. Similar to the hardware implementation, the match criteria are, in fact, controllable. In this approach, they are determined by the way the original pattern is manipulated to produce the technical pattern. Figure 6 shows a screenshot of the GUI dashboard. The UI enables a user to provide inputs to manipulate the original

Fig. 5 Block diagram representing software implementation of EeLADA

#### Fig. 6 EeLADA software implementation graphical user interface

pattern based on the failure signature. A configuration file is then generated out of the UI and transferred to the tester to execute the process. There are three selection panels on the GUI for user inputs. The tester platform determines the format of the configuration file. Fundamentally, there are two steps involved in manipulating the compare vectors in the original pattern. First, the user may choose whether to invert all or partially invert the compare fail cycles according to the failing signature. The last option is to execute no vector inversion. In the second step, the mask select option enables the user to mask out the remaining compare fail vectors (within the reference failed vectors but not inverted in the first step), the remaining compare vectors (not a part of the reference failed vectors), or not mask anything.

| Vectors<br>Vectors mask<br>invert    | None | Mask all other<br>compare vectors<br>(within ref. fail) | Mask all other<br>compare vectors<br>(not within ref. fail) |

|--------------------------------------|------|---------------------------------------------------------|-------------------------------------------------------------|

| Invert all fail cycles               |      |                                                         |                                                             |

| Invert selective                     |      |                                                         |                                                             |

| Invert 1 <sup>st</sup> fail<br>cycle |      |                                                         |                                                             |

| Invert last fail cycle               |      |                                                         |                                                             |

| None                                 |      |                                                         |                                                             |

Most stringent

Least stringent

#### Fig. 7 Variations of technical test pattern

|    |        |   |    |    | IO p | oins |    |    |   |        |   | IO pins |      |    |      |    |    |  |  |

|----|--------|---|----|----|------|------|----|----|---|--------|---|---------|------|----|------|----|----|--|--|

|    |        |   | A0 | A1 | A2   | A3   | A4 | A5 |   |        |   | A0      | A1   | A2 | A3   | A4 | A5 |  |  |

|    |        | 1 | Н  | L  | L    | L    | н  | н  |   | Cycles | 1 | н       | L    | L  | L    | н  | н  |  |  |

|    |        | 2 | Н  | L  | Н    | Н    | н  | L  |   |        | 2 | н       | L->H | н  | н    | н  | L  |  |  |

| SS | es     | 3 | L  | L  | н    | н    | L  | L  |   |        | 3 | L       | Г    | н  | Н    | L  | L  |  |  |

|    | Cycles | 4 | Н  | н  | L    | н    | L  | н  | 7 |        | 4 | н       | Н    | L  | H->L | L  | н  |  |  |

|    | σ[     | 5 | L  | L  | н    | Н    | н  | L  |   | U      | 5 | L       | L    | н  | н    | н  | L  |  |  |

|    |        | 6 | L  | н  | Н    | L    | L  | н  |   |        | 6 | L       | н    | н  | L    | L  | н  |  |  |

|    |        | 7 | Н  | L  | L    | Н    | Н  | н  |   |        | 7 | н       | L    | L  | H->L | н  | н  |  |  |

| (a) |

|-----|

|     |

|     | IO pins |   |    |    |    |    |    |    |   |        |   | IO pins |    |    |    |    |    |  |  |

|-----|---------|---|----|----|----|----|----|----|---|--------|---|---------|----|----|----|----|----|--|--|

|     |         |   | A0 | A1 | A2 | A3 | A4 | A5 |   |        |   | A0      | A1 | A2 | A3 | A4 | A5 |  |  |

|     | Cycles  | 1 | н  | L  | L  | L  | н  | н  |   | Cycles | 1 | н       | L  | L  | L  | н  | Н  |  |  |

|     |         | 2 | н  |    | Н  | н  | н  | L  |   |        | 2 | Н       | X  | Н  | н  | н  | L  |  |  |

|     |         | 3 | L  | L  | н  | н  | L  | L  | Ъ |        | 3 | L       | L  | н  | н  | L  | L  |  |  |

|     |         | 4 | н  | н  | L  | Н  | L  | н  | 7 |        | 4 | Н       | Н  | L  | X  | L  | Н  |  |  |

|     | 5       | 5 | L  | L  | н  | н  | н  | L  |   | ۍ<br>ا | 5 | L       | L  | н  | н  | н  | L  |  |  |

|     |         | 6 | L  | н  | н  | L  | L  | н  |   |        | 6 | L       | н  | н  | L  | L  | н  |  |  |

| (b) |         | 7 | н  | L  | L  | Н  | н  | н  |   |        | 7 | н       | L  | L  | X  | н  | н  |  |  |

Fig. 8 (a) Most-stringent and (b) least-stringent technical test patterns

Figure 7 presents a matrix defining the different variants of compare vector manipulation and their corresponding stringency. As an illustration, Fig. 8(a) and (b) show the case of the most- and least-stringent scenarios, respectively. The compare vectors highlighted in red are failing on a bad IC. Following the most-stringent match criteria, all these compare vectors are inverted in the technical pattern. This is the case described in the beginning of this section. To demonstrate the methodology, the same experiment that was performed earlier following the hardware approach is repeated, but this time applying the software approach. The EeLADA

(a)

(b)

Fig. 9 (a) Conventional LADA signals. (b) EeLADA based on least-stringent technical test pattern

signals obtained are similar to Fig. 4(b). This validates the method.

Consider the least-stringent case next, using another experiment based on some random logic of an IC. The compare vectors are masked in the technical pattern according to a failed IC's failure signature, and the EeLADA signals acquired on a passing IC are shown in Fig. 9(b). Figure 9(a) shows the conventional LADA signals (passto-fail state transition) acquired using the original test pattern for comparison. Some signals appear to be missing

in Fig. 9(b), because laser stimulations at these locations do not result in a fail. This is the effect of masking the compare vectors.

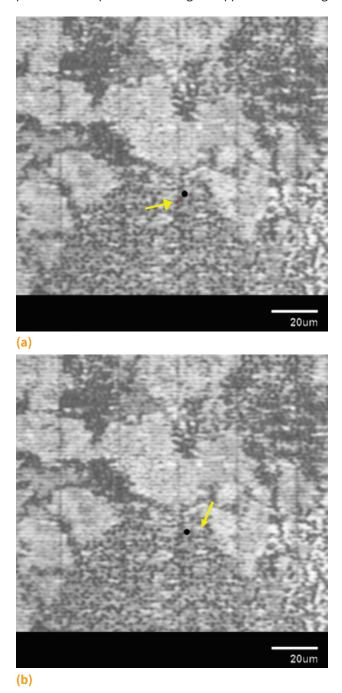

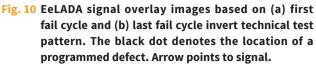

Another experiment was performed by creating a programmed defect in the active area of some random logic using a 1340 nm wavelength laser through the silicon substrate. The device is tested, and the fail log is collected. Figure 10(a) shows the EeLADA overlay image for the case of inverting only the first fail cycle of the failure signature, and Fig. 10(b) shows the case of inverting the last fail cycle on the technical pattern. It should be remembered that EeLADA is performed on a passing IC. The black dot denotes the exact programmed defect location. The arrows pinpoint the EeLADA signals. It is evident that although the signal does not precisely coincide with the defect, the observation within the vicinity of 10 µm is sufficient to guide and achieve physical failure analysis success on the bad die. The results from this experiment demonstrate the potential of employing EeLADA for hard defect localization. More comprehensive studies are necessary in this aspect.

# HARDWARE VERSUS SOFTWARE APPROACH

While both hardware and software approaches are able to realize the concept of filtering LADA signals, it is worth highlighting again that the manner of operation is significantly different. The latter method is not as straightforward, but the outcome is congruent, as evidenced earlier. The idea of matching is more intuitive by using the comparator circuit. For EeLADA inspection time, the hardware approach has a slight advantage, because the dwell time per pixel is shorter since it is no longer necessary to incorporate wait times for the accommodation of synchronizing and pass/fail pulses in a single test loop. However, the flipside in this method lies in the use of cables that may not be suited for IC testing speeds above 50 MHz.

# CONCLUSION

Whenever a LADA event occurs due to a state transition from fail to pass, the signal relevance to the exact failing signature is obvious. However, the reverse is not true. Therefore, signals that arise from a pass-to-fail state transition are more concerning. Normally, they can involve various combinations in terms of failing pins and cycles, be it conventional LADA or TR-LADA. EeLADA is an evolution that resolves this ambiguity to extract relevant signals for analysis. The fundamentals behind EeLADA have been detailed in this article. Although EeLADA appears to be a derivative of LADA, in practice, EeSDL will work as well. As a final takeaway, it is worth a moment to pause and review the custom way IC failures are debugged. Should defect localization always be performed directly on failed dice? The preliminary demonstration of the EeLADA application to hard defect localization is an exemplary example of deviating from this rule of thumb.

#### REFERENCES

- 1. J.A. Rowlette and M.E. Travis: "Critical Timing Analysis in Microprocessors Using Near-IR Laser Assisted Device Alteration (LADA)," *Proc. Int. Test Conf. (ITC)*, 2003, pp. 264-64.

- 2. J.G. Van Hassel and F. Zachariasse: "Product Debug: Speed Problem Related to Unexpected RC Delay," *Proc. Int. Symp. Test. Fail Anal. (ISTFA)*, 2010, pp. 206-10.

- 3. S. Lee et al.: "Marginal Failure Diagnosed with LADA: Case Studies," Proc. Int. Symp. Test. Fail. Anal. (ISTFA), 2014, pp. 367-73.

- 4. A. Douin et al.: "Time Resolved Imaging Using Synchronous Picosecond Photoelectric Laser Stimulation," *Microelectron. Reliab.*, 2006, *46*, pp. 1514-19.

- 5. J. Shaw et al.: "Dual Port RAM MBIST Failure Analysis Using Time Resolved Dynamic Laser Stimulation," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2008, pp. 188-92.

- K. Erington, J. Asquith, and D. Bodoh: "Software Enhanced Time Resolved Laser Assisted Device Alteration with a Non-Pulsed Laser Source," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2009, pp. 43-51.

- 7. D. Bodoh, K. Erington, and K. Dickson: "Root Cause Analysis Techniques Using Picosecond Time Resolved LADA," *Proc. Int. Symp. Test. Fail. Anal. (ISTFA)*, 2014, pp. 82-86.

- S.H. Goh et al.: "Fault Isolation Using Electrically-Enhanced LADA (EeLADA)," *Proc. Int. Symp. Phys. Fail. Anal. Integr. Circuits (IPFA)*, 2015, pp. 572-76.

- S.H. Goh et al.: "Electrically-Enhanced LADA (EeLADA) Technique," Proc. Int. Symp. Test. Fail. Anal. (ISTFA), 2015, pp. 9-15.

ABOUT THE AUTHORS

**S.H. Goh** received his B.Eng, and Ph.D. degrees in electrical and computer engineering from the National University of Singapore. His doctorate research on simulation and implementation of the aplanatic refractive solid immersion lens was awarded a conference Best Paper and was part of a team project that received the 2009 Singapore President's Technology Award. Dr. Goh is currently with Globalfoundries, Product, Test, and Failure Analysis Division, Singapore, where he leads a team responsible for product failure diagnostics and advanced methodologies to accelerate yield ramp. His main focus is on development of dynamic fault isolation techniques, wafer-level fault isolation methods, and leveraging cross-functional domain knowledge of design, test, and failure analysis to

enhance yield learning. His work has been published in conference proceedings and journals. Dr. Goh is also an active contributor to IPFA and ISTFA technical committees.

# **ABOUT THE AUTHORS (continued)**

**B.L. Yeoh** graduated from the University of Technology, Malaysia, with a B.E. degree in electrical engineering. In 2006, he joined Intel Microelectronics Malaysia as a failure analysis engineer, where he specialized in memory testing and failure analysis during his five-year tenure. He is currently employed as a Member of the Technical Staff at Globalfoundries Singapore. His field of interest focuses on device fault isolation using a wide range of industry-standard electrical failure analysis tools, such as photon emission microscopy and laser scanning microscopy techniques (OBIRCH, TIVA, dynamic laser stimulation, etc.). His current research interests focus on exploring soft defect localization and laser-assisted device alteration techniques for different failure-type diagnostics in the semiconductor industry.

**G.F. You** holds a B.S. degree in physics from Fu Dan University, China; an M.Eng. degree in electrical engineering from Nanyang Technology University, Singapore; and a Ph.D. degree in the same field from the National University of Singapore (NUS). Currently, he specializes in wafer-level tester-based failure debug in Globalfoundries' Product/Test and Yield Engineering Department, Singapore. His experiences include dynamic fault isolation techniques, such as frequency mapping and soft failure localization. Prior to joining Globalfoundries, Dr. You worked as a research fellow at NUS.

**Y.H. Chan** graduated from the National University of Singapore with an M.Eng. in electrical and electronic engineering. He was a test engineer with AMD from 2005 to 2008 before joining Globalfoundries as a diagnostic test lead. Mr. Chan has more than ten years of experience in semiconductor testing, specializing in automated test equipment (ATE) and burn-in test solution development, implementation, and debug. He is very familiar with ATE test solution development on the Advantest, Teradyne, and LTX family of testers, for both engineering sort testing and advanced coding methodologies for dynamic electrical failure analysis applications. He is also a programmer familiar with C++ and VBA coding. His current research interests focus on test methodology optimization for test-time reduction and multidimensional solution-search algorithms.

**Zhao Lin** received her B.E. degree in electrical engineering from the National University of Singapore in 2015. She then joined Globalfoundries' Singapore Product/Test and Yield Engineering Department as a test development engineer. She works on diagnostic testing and focuses on failure characterization with various tester platforms, such as HP93K, Teradyne Uflex and J750, and Credence D-10. Ms. Lin is pursuing an M.S. degree with a specialization in nanoelectronics at the National University of Singapore.

**Jeffrey Lam** received his B.S. and M.S. degrees in chemical engineering from the University of California Berkeley and the University of California Davis in 1979 and 1981, respectively. He obtained a second M.S. degree in electrical engineering and computer science from the University of Santa Clara in 1986. In 2014, he received his Ph.D. from the school of mathematics and physics at Nanyang Technological University. Dr. Lam is currently a Vice President at Globalfoundries, Singapore, where he is in charge of the Product/Test and Yield Engineering Department in Technology Development. He possesses more than 35 years of experience in FA, design, product/yield engineering, and test

development. Dr. Lam has 7 technical patents and more than 20 publications. He has also been the chairman of the SEMI SGP Product and Test Committee since 2009 and an adjunct associate professor at the National University of Singapore.

**C.M. Chua** received his Bachelor's and Master's degrees in engineering from the National University of Singapore in 1988 and 1990, respectively. He is the Chief Executive Officer of Semicaps Corporation, and his current responsibilities include overseeing the general operations of the companies within the Semicaps Corporation Group.

ELECTRONIC DEVICE FAILURE ANALYSIS | VOLUME 18 NO.

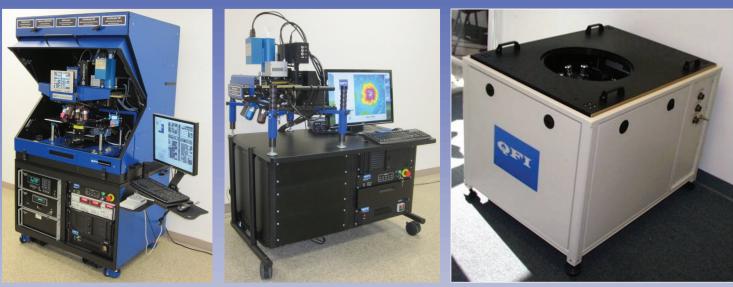

# **QuantumScope**<sup>TM</sup> Failure Analysis Microscopes

### FA engineers need proper tools in order to locate IC defects:

- ohmic shorts

- impedance issues

- leakage currents

- leaky capacitors

- oxide defects

- damaged junctions

- resistive vias

- CMOS latch up

- ESD damage

- dynamic failures

# QFI suggests maximizing your defect capture rate... NOT your capital expenditure rate.

QuantumScope<sup>™</sup> integrates XIVA<sup>™</sup> LSIM, Thermal-HS hot spot detection, and emmi<sup>™</sup> photoemission into a single, high-performance, microscope platform. Semiconductor FA is more efficient and more accurate when the DUT remains mounted in a single diagnostic tool during all three of these FA microscope techniques. QuantumScope<sup>™</sup> eliminates the need for multiple separate systems, freeing capital for other requirements. QFI systems are modular in design and generally compatible with field upgrade.

**Quantum Focus Instruments Corporation**

2385 La Mirada Drive • Vista CA 92081 Phone: +1 (760) 599-1122 Fax: +1 (760) 599-1242 e-mail: sales@quantumfocus.com http://www.guantumfocus.com

# MANAGEABILITY CHALLENGES FOR INTERNET OF THINGS

Yen-Kuang Chen, Principal Engineer, Intel Corporation, and Associate Director, Intel-NTU Connected Context Computing Center y.k.chen@ieee.org

here is no longer much argument around the Internet of Things (IoT) concept as the "next big thing," but consensus remains elusive around the next level of questions and discussion: Why is the IoT going to be so great, and what are the obstacles to achieving that vision?

The IoT is already delivering valuable benefits in the nascent stage of its development. However, I would argue that "IoT Version 1.0" has not yet been realized, and the magnitude of this revolutionary innovation will not become clear until then.

Getting to that point will require addressing a variety of user pain points, perhaps the most glaring of which is device failure. Mainstream adoption of and reliance on the IoT demands a scenario in which one or more disparate devices may fail but the overall system continues to function. Perhaps the system would not function as well as when the failed devices were operational, but it would continue. In the meantime, the failed device could be recognized and repaired without the user experiencing a disruption in service and with a return to optimal system performance.

In addition to more functionally reliable devices, IoT 1.0 will require an intelligent middleware layer for multivendor device management. Achieving such a layer will require global collaboration across the IoT's diverse stakeholders.

# WHEN WILL THE IOT REALLY BE THE IOT?

I began working on the IoT six years ago, and at that time, I didn't have a clear definition of what the IoT is or would be.

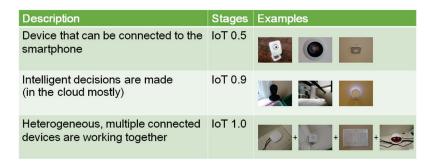

Even today, different people have different definitions of the IoT. For some, the IoT is having things connected to a smartphone and enabling capabilities such as remotely locking/unlocking the front door. For others, the IoT is having a device connected to the internet, streaming data to the cloud, and having the cloud perform intelligent analytics to help humans make intelligent decisions. However, such definitions are still predicated on the notion of a small number of devices connected through the internet to individual humans, who, at the very least, are kept in the loop for all the real decision-making.

My definition of the true IoT—IoT 1.0, if you will—is when heterogeneous, multiple connected devices are working together to our benefit and without us having to make all of the decisions (Fig. 1). The IoT will deliver more benefits with more and more devices working together without human interaction, which both naturally impedes IoT scalability and adds complexity to our lives.

For example, mental wellness is an area that especially interests me. In the IoT 1.0, devices that measure various bio signals, such as heart rate and temperature, could be

Fig. 1 When heterogeneous, multiple connected devices are working together without humans making all of the decisions, we will attain IoT 1.0.

in used in combination with other intelligence to better understand a person's mental as well as physical health state in relation to various stress factors. If a wearable sensor was linked with the user's calendar, the system may be able to connect the dots and realize that the reason a user is stressed is because there is a key meeting coming up in 15 minutes. Without the link to the calendar, while the device may be able to do numerous measurements of the human body, the overall system would not have any context for the results.

Another compelling use for the IoT 1.0 vision is the capability for devices to work together through the system to make someone (like me) more comfortable on a day when they are ill. Perhaps a device would note that my skin temperature is rising, detecting a fever, and know that I prefer a warmer room when I am feverish. With the IoT 1.0 providing a link between the device monitoring my temperature and the devices regulating climate control in my home, the system could adjust my environment to make it more comfortable without any direct interaction from me.

With the notion of multivendor, heterogeneous devices linked to one another and able to act in concert, the benefits of the IoT 1.0 for humans become quite easy to imagine. For example, we all have numerous keys, and many of us have garage-door openers, but do we really need these things in the emerging IoT world? Could a system recognize us and let us into our homes securely and conveniently without a key or garage-door opener? It would be great if, when my car approached the driveway of my home, the system sensed ony approach and automatically opened the garage door. When I leave the house, it should be able to close the door, lock it automatically, and turn on the home-security systems, because it knows I am gone.

# "MY DEFINITION OF THE TRUE IoT—IoT 1.0, IF YOU WILL—IS WHEN HETEROGENEOUS, MULTIPLE CONNECTED DEVICES ARE WORKING TOGETHER TO OUR BENEFIT AND WITHOUT US HAVING TO MAKE ALL OF THE DECISIONS. "

(lighting, electric vehicles, energy efficiency, garden and home appliances), healthcare and assisted living, audio/ visual services, entertainment, and so on, the benefits to such a vision of the IoT are clear. However, challenges must be addressed to achieve an IoT 1.0 in which heterogeneous, multiple connected devices work together to my benefit without me controlling everything.

The single most problematic set of pain points inhibiting realization of the IoT 1.0 vision today may be device failures. Communication and battery issues can undo whole systems and their potential benefits. Plus, there's usually a limited user interface for debugging. Without a better solution for managing and adapting to device failure, the IoT will continue to be more of a technological novelty or curiosity than a major underpinning of daily life around the globe.

# **MY IoT@HOME**

I recently counted over 100 commercially available connected devices in my house. *One hundred!* Presence sensors, motion sensors, electronic lock, lighting control, water sensors, garage-door opener, cameras, sirens, smart meters, smoke detectors, and so on (Fig. 2). For example, I have a very heavily connected and guarded front porch: four cameras, three motion sensors, three infrared lights,

Across security and access control, utility management

Fig. 2 In my IoT@Home, apps and devices provide benefits, but such a large number of devices creates the issue of device failure, which requires a significant amount of debugging time.

#### edfas.org

and three open/close sensors. In addition, I use more than 20 apps in my home.

So many devices and so many apps unquestionably bring me a great deal of personal benefit; however, so many devices and apps create issues, too. The biggest challenge I face in my personal "IoT@Home" is that I constantly need to fix one thing or another. Each device has an approximate average failure rate of once per year. So, if just one device fails per week, that leaves me in a regular mode of debugging my system, and that keeps me really, really unhappy.

Device failures currently comprise a problem with only 100 devices in my home, but what happens when the forecasts for IoT proliferation come to pass and I have 300 or 400 connected devices in my home? Most home users simply are not interested or are incapable of dealing with each individual fault across devices in a system that is so quickly growing in complexity, interconnectivity, and the sheer number of devices.

# TOWARD A SOFTWARE-DEFINED IoT

Implicit in the issue of device failures are at least a couple of calls to action for the industry that is building out the IoT 1.0 around the world. Device manufacturers can strive to make more-reliable devices, and, of course, they already are and always will be striving to do so. Certainly, this is a necessary pursuit.

However, even if devices are made more reliable, the truth is that some rate of device failure is inevitable. The IoT 1.0 will deliver its greatest benefits when users are able to experience the IoT while remaining almost naïve to the applications and devices that enable the experience. The system should still be able to operate, even when individual devices run into a faulty state.

This need tees up the requirement for an intelligent middleware to minimize human effort and automatically monitor and control the overall system, recognize individual failures, and hand over capabilities among devices as necessary. There needs to be an intelligent mapping of devices within the virtual space of the IoT 1.0. This cyberphysical intersection will be critical to a resilient system.

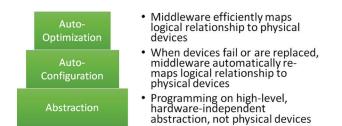

At the Intel-NTU Connected Context Computing Center, for example, we are working on a proactive management framework, "WuKong," that works to limit IoT user interaction to simply sending requests to applications and defining context and high-level policy. The new middleware layer intelligently maps the logical relationship to physical devices, and, when devices fail or are replaced, the middleware automatically re-maps a logical relationship to the physical devices (Fig. 3).

Fig. 3 Middleware will enable a software-defined IoT, minimizing human intervention.

Furthermore, programming is performed on high-level, hardware-independent construction—not the specific physical devices—so that programs can be written once and then run everywhere across the IoT. Moving the devices/services around becomes easier. Finally, if the user's intention is properly communicated to the middleware, then the user should not be concerned with finely adjusting the device sensitivities.

Sensitivity is another area of pain. For example, today a motion sensor set too sensitive on my front porch may detect a car passing on the street in front of my home and trigger useless picture-taking by my home-security system; the same motion sensor set not sensitive enough may ignore someone walking on my front yard. With a better, more intelligent middleware that understands the security goals of the user, the middleware should make sensitivity decisions per device based on the user's greater system-level intention, as opposed to simple, preset thresholds for each device.

Such a middleware layer is being designed ultimately to enable a software-defined IoT that would minimize human intervention and relieve the pain point of managing devices. It is one of the places where the IoT demands open, cross-discipline collaboration to rapidly and fully bring about the benefits envisioned. I invite you to visit http://iot.ieee.org/iot-scenarios.html to weigh in on the Intel-NTU Connected Context Computing Center's concept for intelligent IoT middleware and other emerging IoT scenarios.

### CONCLUSION

Collaboration is the key for a large system such as the IoT 1.0 to function optimally. Many different components across diverse application domains must be able to seamlessly interoperate, and each application domain has insights that must be taken into account for the greatest potential benefit of the IoT to be realized. Technologies must and will advance so that the system is still able to operate even in the reality of device failure.

# **CALL TO ACTION**

IEEE is a proven forum for stakeholders globally to collaborate for the benefit of humanity. IEEE is the world's largest professional association dedicated to advancing technological innovation and excellence for the benefit of humanity, with more than 426,000 members in more than 160 countries (over 50% of whom are from outside the United States).

The IEEE IoT Initiative (http://iot.ieee.org), for example, has released a document intended to establish a baseline definition of IoT in the context of applications that range from small, localized systems constrained to a specific location, to a large global system that is geographically distributed and composed of complex subsystems. The IEEE IoT Initiative invites global involvement from parties interested in advancing the definitions within the IoT.

In addition, the IEEE Standards Association has a number of standards, projects, and events that are directly related to creating the environment needed for a vibrant IoT (http://standards.ieee.org/innovate/iot/index.html).

Collaboration through such globally open activities will help ensure that the IoT indeed turns out to be the "next big thing."

# **ABOUT THE AUTHOR**

**Yen-Kuang Chen** is a principal engineer at Intel Corporation. His research areas span from emerging applications that can utilize the true potential of the IoT to computer architecture that can embrace emerging applications. Dr. Chen has 60+ U.S. patents, 20+ pending patent applications, and 90+ technical publications. He is one of the key contributors to Supplemental Streaming SIMD Extension 3 and Advanced Vector Extension in Intel microprocessors. Dr. Chen has served as a program committee member of more than 50 international conferences on IoT, multimedia, video communication, image processing, VLSI circuits and systems, parallel processing, and software opti-

mization. He is a steering committee member of *IEEE Internet of Things Journal*, the past chair of the IoT Special Interest Group of the IEEE Signal Processing Society, the Editor-in-Chief of *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, and the Distinguished Lecturer of the IEEE Circuits and Systems Society. Dr. Chen received his Ph.D. from Princeton University and is an IEEE Fellow.

# **EDFAS MEMBERSHIP**

Whether networking at events or accessing information through *EDFA*, ISTFA proceedings, or journals, our members have the edge. Now it's time to introduce EDFAS to others in the industry who would like to take advantage of these careerenhancing benefits. Help us help the industry by expanding our membership and offering others the same exceptional access to information and networking that sets EDFAS apart. To reacquaint yourself with and introduce others to the EDFAS member benefits, visit asminternational.org/web/edfas/membership.

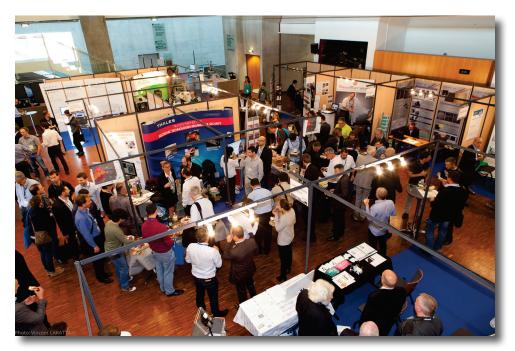

**ESREF** opening session

# **ESREF 2015 IN TOULOUSE**

Marise Bafleur, ESREF 2015 Conference Chair Philippe Perdu, ESREF 2015 Conference Co-Chair marise@laas.fr philippe.perdu.cnes@gmail.com

he 26th European Symposium on Reliability of Electron Devices, Failure Physics and Analysis (ESREF 2015) was held October 5 to 9, 2015, in Toulouse, France. This was the first time the conference was hosted by the city of Toulouse, which is a world center for aeronautics (Airbus), the European capital of the space industry, and France's leader for embedded electronic systems. The ESREF 2015 Organizing Committee, led by Conference Chair Marise Bafleur (LAAS, France), assembled more than 100 volunteers to successfully stage the conference, which saw a record attendance of more than 400.

This international symposium continued to focus on recent developments and future directions in quality and reliability management of materials, devices, and circuits for micro-, nano-, and optoelectronics. It provided a European forum for developing all aspects of reliability management and innovative analysis techniques for present and future electronic applications through twelve sessions:

- Session A: Quality and Reliability Assessment—techniques and methods for devices and systems

- Session B1: Silicon Technologies and Nanoelectronics hot carriers, high-k, gate materials

- Session B3: Silicon Technologies and Nanoelectronics electrostatic discharge, latch-up, radiation effects

- Session C: Failure Analysis

- Session D1: Microwave and Power Wide-Bandgap Semiconductor Devices

**Poster session**

- Session D2: Photonic

- Session D3: Photovoltaic and Organic Devices

- Session E1: Packaging and Assembly

- Session E2: MEMS, MOEMS, NEMS, and Nano-Objects

- Session F: Power Devices

- Session G: Space, Aeronautic, and Embedded Systems

- Session H: European FIB User Group (EFUG)

To draw new attendees and offer returnees an attractive conference, the organizers expanded the topical structure of the conference. Each topic was embedded with invited papers, tutorials, workshops, an oral session, a posted area for the oral presenters during the session breaks, and a poster session. The layout of the conference was set up to allow each attendee to build his or her optimal schedule by topic or by specific interest without overlaps. For example, it was possible to follow an expert training track with two keynotes, ten tutorials, and nine invited papers. Hélène Fremont and François Marc (IMS, France), Technical Program Chairs; Peter Jacob (EMPA, Switzerland) and Giovanni Busatto (University of Cassino, Italy), Tutorial Chairs; and Mauro Ciappa (ETH Zürich, Switzerland), Thomas Zirilli (Freescale, France), and Fulvio Infante (Intraspec Technologies), Workshop Chairs, did an incredible job of building the best topical tracks.

Local attendance was also targeted. The Local Events Committee, chaired by Alain Bensoussan and André Durier (IRT Saint Exupéry, France), brought regional inputs to foster local attendance on aeronautic, space, and embedded systems, which was a hot topic during the conference. An opportunity was also provided for students from the area to participate in a Student Research "Speed-Dating" session. The award for the best one, "Evidence for Proton Diffusion in H+ Irradiated DFB and VCSEL Commercial Laser Diodes" by Giulia Marcello (Department of Electrical and Electronic Engineering, University of Cagliari, Italy), was presented during the gala dinner. Another boost for local attendance was a specific fee schedule for companies, with the capability to split the fees into half-days.

The ten workshops and the exhibition at the heart of the conference provided enhanced networking activities in a pleasant atmosphere. Interaction between the attendees and the 21 exhibitors was optimized by integration of exhibitor flash presentations to underline a specific technique. These flash presentations were fully integrated into the failure analysis track. All of the catering (coffee break, lunches, and cocktails on Monday) was held at

**The ESREF exhibition**

the Expo, and the twelve Expo-only hours presented the opportunity for attendees to network with key vendors representing the core business area in the fields of reliability and failure physics and analysis of electron devices and systems. Tuesday's cocktails at Capitole, the Toulouse city hall, and the gala dinner at the space museum (Cite de l'espace) were also excellent networking opportunities.

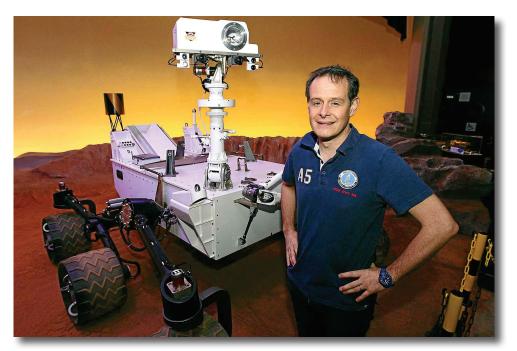

With up to four parallel tracks, the conference was very dense with rich content. During Monday afternoon's opening session, the first keynote speaker, Sylvestre Maurice (IRAP, France), presented a fascinating talk entitled "ChemCam Instrument on the Curiosity Rover: From R&D to Operations on Mars; Be Reliable or Die." The ChemCam project started as an R&D program at the French space agency CNES in 2001, was selected by NASA in 2005, was launched in 2011, and has operated on the Curiosity rover on Mars since 2012. It consists of a high-energy laser that, at a distance, creates plasma on Mars' soils and rocks to infer their elemental composition. He presented how the anomaly of a laser diode used for instrument autofocus was handled. The failure of this diode did not allow adjustment of the ablation laser pulses on rocks, forcing operators to multiply them. The software solution developed by the ChemCam team achieved autofocus by another process, thus restoring the entire system's agility. This feedback will be incorporated into the next SuperCam instrument.

The second keynote, by Ramesh Karri (Polytechnic Institute of New York University), focused on a very important topic, "Towards Hardware Cyber Security." Hardware security and trust are important design objectives, similar to power, performance, reliability, and testability. He highlighted why hardware security and trust are important objectives from the economics, security, and safety perspectives. Important messages from this talk included: (1) understanding simple "gotchas" when traditional design for test (DFT), test, and validation techniques are used (scan chains, JTAG, system-on-chip test, assertionbased validation); (2) understanding how traditional DFT, test, and validation techniques can be used to improve hardware security and trust; and (3) understanding "design-for-trust" approaches that can provide testability without compromising security and trust.

The opening session concluded with the Best Papers from sister conferences:

ISTFA 2014 Outstanding Paper: "Localization of Weak Points in Thin Dielectric Layers by Electron Beam Absorbed Current (EBAC) Imaging" by Jörg Jatzkowski, Michél Simon-Najasek, and Frank Altmann (Center for Applied Microstructure Diagnostics, Fraunhofer Institute for Mechanics of Materials, Halle, Germany)

- IPFA 2015 Best Paper: "UTB GeOI 6T SRAM Cell and Sense Amplifier Considering BTI Reliability" by Vita Pi-Ho Hu, Pin Su, and Ching-Te Chuang (Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Taiwan)

- IRPS 2015 Best Paper: "Platform Qualification Methodology: Face Recognition" by Ghadeer Antanius, Rutvi Trivedi, and Robert Kwasnick (Intel Corporation, USA)

Monday ended with a buffet served in the exhibition area.

Catering in the exhibition area

It is not possible to include all the topical tracks (up to four) held from Tuesday to Friday, but the following describes the one dedicated to failure analysis. It began with the invited speaker, Ludwig Balk (University of Wuppertal, Germany). In his talk, "EOBT: From Past to Future," Professor Balk reviewed optical and electron beam techniques and provided a view into future development requirements.

Next came the regular papers and posters session, with many interesting and varied subjects:

"Nitrogen-Vacancy Centers in Diamond for Current Imaging at the Redistributive Layer Level of Integrated Circuits"

Cocktails in the Salle des Illustres at Capitole, the Toulouse city hall

- "Scanning Acoustic GHz-Microscopy versus Conventional SAM for Advanced Assessment of Ball Bond and Metal Interfaces in Microelectronic Devices"

- "New I.R. Thermography Methodology for Failure Analysis on Tantalum Capacitors"

- Comprehensive 2-D Carrier Profiling of Low Doping Region by High-Sensitivity Scanning Spreading Resistance Microscopy (SSRM) for Power Device Applications"

- "Unsupervised Learning for Signal Mapping in Dynamic Photon Emission"

- "Use of a Silicon Drift Detector for Cathodoluminescence Detection"

- "Failure Analysis on Recovering Low Resistive Via in Mixed-Mode Device"

- "RF Functional-Based Complete FA Flow"

- "Improvement of Signal-to-Noise Ratio in Electro-Optical Probing Technique by Wavelets Filtering"

- "Visualization of Gate-Bias-Dependent Carrier Distribution in SiC Power-MOSFET Using Super-Higher-Order Scanning Nonlinear Dielectric Microscopy"

- "Electrical Model of an Inverter Body Biased Structure in Triple-Well Technology under Pulsed Photoelectric Laser Stimulation"

- "Die Crack Failure Mechanism Investigations Depending on the Time of Failure"

- "Top-Down Delayering to Expose Large Inspection Area on Die Side-Edge with Platinum (Pt) Deposition Technique"

- "Auger Electron Spectroscopy Characterization of Ti/NiV/Ag Multilayer Back-Metal for Monitoring of Ni Migration on Ag Surface"

- "Magnetic Imaging for Resistive, Capacitive, and Inductive Devices: From Theory to Piezo Actuator Failure Localization"

- "Microscopic Investigation of SiO<sub>2</sub>/SiC Interface Using Super-Higher-Order Scanning Nonlinear Dielectric Microscopy"

- "Thermoreflectance Mapping Observation of Power MOSFET under UIS Avalanche Breakdown Condition"

- "Characteristics and Early Failure of PCB Embedded Power Electronics"

- "Fault Isolation in a Case Study of Failure Analysis on Metal-Insulator-Metal Capacitor Structures"

- "High-Resolution X-Ray Computed Tomography of Through-Silicon Vias for RF MEMS Integrated Passive Device Applications"

- "Compact Thermal Modeling of Spin Transfer Torque Magnetic Tunnel Junction"

The failure analysis track also had three embedded workshops:

- Advanced tools and techniques flash presentations: mini-workshops on methods and tools for failure

- "Latent Gate Oxide Defects Case Studies"

analysis and reliability; fault isolation and defect localization; sample preparation; nondestructive testing and physical characterization; and nanoscale electrical measurement

- Technical seminar: "Chip-Level Advanced Failure Analysis Case Studies," organized by gold sponsor Sector Technologies

- EUFANET Workshop, organized by Jérome Touzel (Infineon, Germany) and Olivier Crépel (AIRBUS Group Innovations, France)

The failure analysis track concluded Wednesday morning with the EFUG session, which had the following interesting presentations:

- "Focused High- and Low-Energy Ion Milling for TEM Specimens"

- "TEM Sample Preparation of an SEM Cross Section Using Electron Beam-Induced Deposition of Carbon"

- "Fabrication of Advanced Probes for Atomic Force Microscopy Using Focused Ion Beam"

- "Plasma FIB: Enlarge Your Field of View and Your Field of Applications"

- "Formation of Coupled Cavities in Quantum Cascade Lasers Using Focused Ion Beam Milling"

This session was followed by the EFUG Workshop, organized by Hugo Bender (IMEC, Belgium).

At the end of the conference, four awards were made:

• *Best Paper:* "System-Level Process-Voltage-Temperature Variation-Aware Reliability Simulator Using a Unified Novel Gate-Delay Model for BTI, HCI, and GOBD" by Taizhi Liu, Chang-Chih Chen, Soonyoung Cha, and Linda Milor. This paper will be presented at the 27th IEEE International Reliability Physics Symposium (IRPS 2016) in Pasadena, Calif.

- *Best Paper:* "Effects of Buffer Compensation Strategies on the Electrical Performance and RF Reliability of AlGaN/GaN HEMTs" by David Bisi et al. This paper will be presented at the 23rd International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA 2016) in Singapore.

- Best Paper: "Unusual Defects Generated by Wafer Sawing: An Update, Including Pick & Place Processing" by Peter Jacob. This paper will be presented at the 42nd International Symposium for Testing and Failure Analysis (ISTFA 2016) in Fort Worth, Texas.

- *Best Poster:* "A Way to Implement the Electro-Optical Technique to Inertial MEMS" by Kevin Melendez et al.

This review cannot end without a specific mention of the pre- and postconference program with lab tours. The Laboratory for Analysis and Architecture of Systems (LAAS) lab tour on Monday morning included: